Tässä viestissä opimme rakentamaan NOT-, AND-, NAND-, OR- ja NOR-logiikkaportteja käyttämällä diskreettejä transistoreita. Transistorilogiikkaporttien käytön tärkein etu on, että ne voivat toimia jopa 1,5 V:n jännitteillä.

Joissakin elektronisissa sovelluksissa käytettävissä oleva jännite saattaa olla riittämätön TTL- tai jopa CMOS-IC:ien tehoon. Tämä pätee erityisesti paristoilla toimiviin laitteisiin. Epäilemättä sinulla on aina 3 voltin logiikka-IC-vaihtoehto. Nämä eivät kuitenkaan aina ole helposti harrastajan tai kokeilijan ulottuvilla, eivätkä ne toimi määriteltyjen jännitemäärittelyjen alapuolella (yleensä alle 2,5 voltin tasavirta).

Lisäksi akkukäyttöisessä sovelluksessa voi olla tilaa vain yhdelle 1,5 voltin akulle. No, mitä aiot sitten tehdä? Yleensä IC-logiikkaportit voitaisiin korvata transistorisoiduilla logiikkaporteilla. Jokaista logiikkaporttia varten tarvitaan yleensä vain pari transistoria, ja tyypilliseen NOT-gate-invertterilogiikkaan tarvitaan vain yksi transistori.

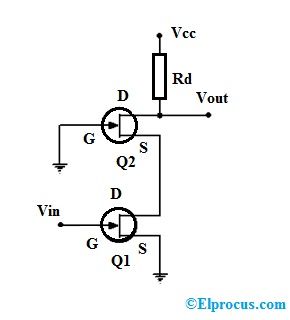

FETit versus bipolaarinen transistori

Kenttätehotransistorit (FET) vs bipolaariset transistorit : mikä on parempi vaihtoehto pienjännitelogiikkapiireille? Yksi hieno ominaisuus FAKTAT on, että niiden 'on' vastus on uskomattoman alhainen. Lisäksi ne tarvitsevat erittäin alhaisen hilakäynnistysvirran.

Niillä on kuitenkin yksi rajoitus erittäin pienijännitesovelluksissa. Tyypillisesti hilajännitteen raja on yksi voltti tai niin. Lisäksi käytettävissä oleva jännite voi laskea FETin optimaalisen toiminta-alueen alapuolelle, jos hilaan on kiinnitetty virtaa rajoittava tai alasvetovastus.

Sitä vastoin bipolaarisilla kytkentätransistoreilla on etu äärimmäisen matalajännitteisissä yhden akun sovelluksissa, koska ne tarvitsevat vain 0,6 - 0,7 volttia kytkeytyäkseen päälle.

Lisäksi suurin osa tavallisista FETeista, joita myydään yleensä kuplapakkauksissa lähimmässä elektroniikkaliikkeessä, ovat usein kalliimpia kuin bipolaaritransistorit. Myös bipolaaritransistoreiden bulkkipaketti voitiin yleensä ostaa FET-parin hinnalla.

FET-käsittely vaatii huomattavasti enemmän varovaisuutta kuin bipolaarinen transistorin käsittely. Sähköstaattinen ja yleinen kokeellinen väärinkäyttö tekevät FET:istä erityisen alttiita vaurioille. Poltetut komponentit voivat pilata nautinnollisen, luovan kokeilu- tai innovaatioillan, unohtamatta virheenkorjauksen emotionaalista tuskaa.

Transistorien kytkemisen perusteet

Tässä artikkelissa selostetut logiikkapiiriesimerkit käyttävät bipolaarisia NPN-transistoreita, koska ne ovat edullisia eivätkä vaadi erityistä käsittelyä. Jotta vältetään laitteen tai sitä tukevien osien vahingoittuminen, on suoritettava asianmukaiset turvatoimenpiteet ennen piirin kytkemistä.

Vaikka piirimme ovat pääosin keskittyneet Bipolar Junction Transistoreihin (BJT), ne olisi voitu yhtä hyvin rakentaa käyttämällä FET-tekniikkaa.

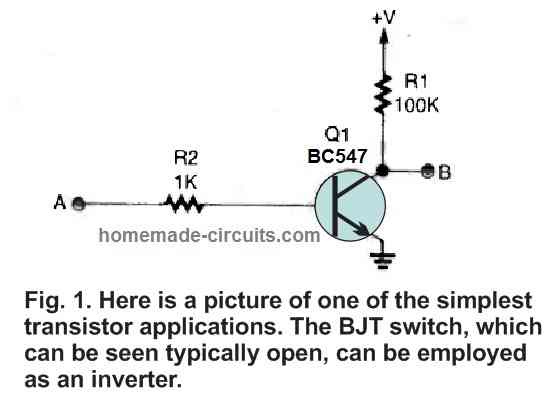

Peruskytkinpiiri on yksinkertainen transistorisovellus, joka on yksi helpoimmista malleista.

NOT-portin tekeminen yhdellä transistorilla

Transistorikytkimen kaavio on esitetty kuvassa 1. Riippuen siitä, kuinka se on toteutettu tietyssä sovelluksessa, kytkin voidaan nähdä joko matalalla pidettynä tai normaalisti auki.

Yksinkertainen NOT-portin invertterin logiikkaportti voidaan luoda kuvassa 1 esitetyllä suoraviivaisella kytkentäpiirillä (jossa piste A on tulo). NOT-portti toimii siten, että jos transistorin kannalle (piste A; Q1) ei ole DC-esijännitettä, se pysyy suljettuna, mikä johtaa korkeaan tai loogiseen 1:een (sama V+-taso) lähdössä ( kohta B).

Transistori kuitenkin aktivoituu, kun oikea esijännite tarjotaan Q1:n kannalle, mikä painaa piirin ulostulon matalalle tai logiikka 0:lle (lähes nollapotentiaali). Transistori, nimeltään Q1, on yleiskäyttöinen bipolaarinen transistori tai BC547, jota käytetään tyypillisesti pienitehoisissa kytkentä- ja vahvistinsovelluksissa.

Mikä tahansa sitä vastaava transistori (kuten 2N2222, 2N4401 jne.) toimisi. R1:n ja R2:n arvot valittiin kompromissin saavuttamiseksi alhaisen virrankulutuksen ja yhteensopivuuden välillä. Kaikissa malleissa vastukset ovat 1/4 wattia, 5 % yksikköä.

Syöttöjännite on säädettävissä välillä 1,4 - 6 volttia DC. Huomaa, että piiri voi toimia puskurina, kun kuormitusvastus ja lähtöliitäntä siirretään transistorin emitteriin.

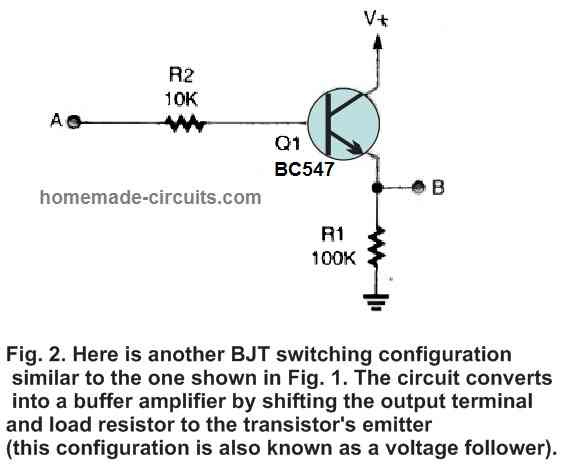

Puskuriportin tekeminen yhdellä BC547 BJT:llä

Jänniteseuraaja tai puskurivahvistin on eräänlainen looginen kytkentäkonfiguraatio, joka on identtinen kuvassa 2 esitetyn kanssa. On huomattava, että kuormitusvastus ja lähtöliitin on siirretty transistorin kollektorista sen emitteriin tässä piirissä, joka on ensisijainen ero tämän ja kuvassa 1 esitetyn mallin välillä.

Transistorin toimintaa voidaan myös 'kääntää' siirtämällä kuormitusvastus ja lähtöliitin BJT:n toiseen päähän.

Toisin sanoen, kun piirin tuloon ei anneta esijännitettä, piirin lähtö jää alhaiseksi; kuitenkin, kun riittävän jännitteinen bias syötetään piirin tuloon, piirin lähtö muuttuu korkeaksi. (Se on täsmälleen päinvastoin kuin aikaisemmassa piirissä.)

Kaksituloisten logiikkaporttien suunnittelu transistoreilla

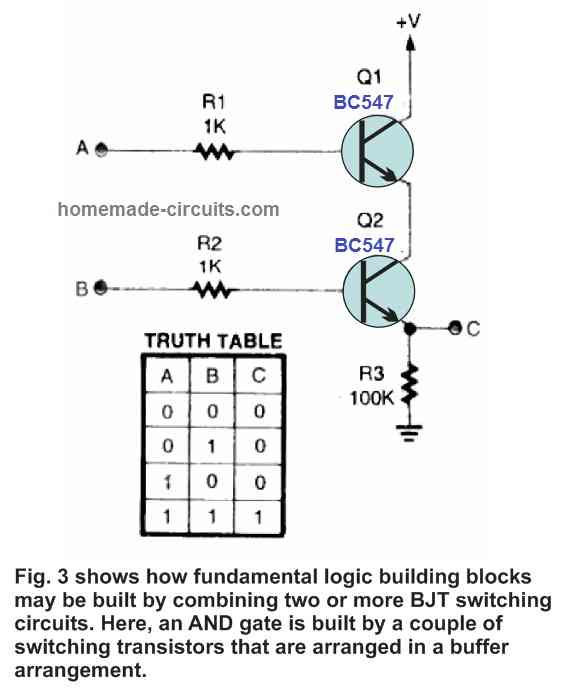

JA portti käyttäen kahta transistoria

Kuva 3 havainnollistaa, kuinka peruskaksituloinen JA-portti voidaan luoda käyttämällä puskuriparia, sekä kyseisen portin totuustaulukko. Totuustaulukko havainnollistaa, mitä tulostulokset olisivat kullekin erilliselle syötejoukolle. Pisteitä A ja B käytetään piirin tuloina ja pistettä C toimii piirin lähtönä.

On tärkeää huomata totuustaulukosta, että vain yksi tuloparametrisarja johtaa loogisen korkean lähtösignaalin, kun taas kaikki muut tuloyhdistelmät johtavat loogisesti matalaan ulostuloon. Kuvan 3 JA-portin lähtö jää hieman V+:n alapuolelle, kun se kääntyy korkeaksi.

Tämä johtuu jännitehäviöstä kahden transistorin (Q1 ja Q2) välillä.

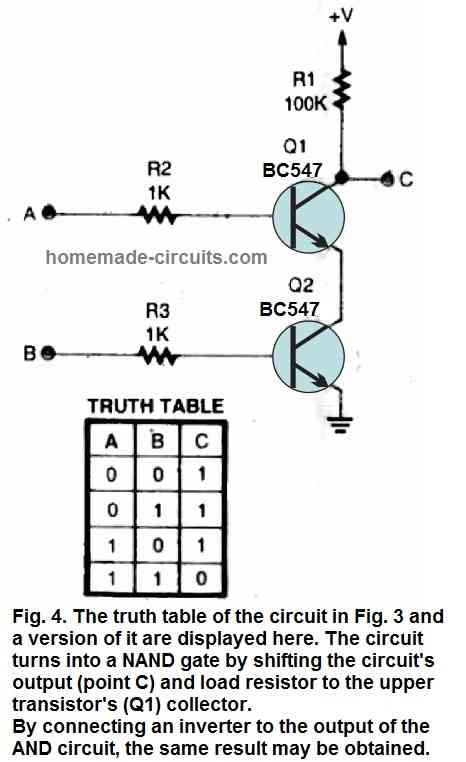

NAND-portti käyttäen kahta transistoria

Toinen kuvion 3 piirin muunnelma ja siihen liittyvä totuustaulukko on esitetty kuvassa 4. Piiri muuttuu EI-JA-portiksi siirtämällä lähtö (piste C) ja lähtövastus ylemmän transistorin (Q1) kollektorille.

Koska sekä Q1 että Q2 on kytkettävä PÄÄLLE R1:n alapuolen vetämiseksi maahan, jännitehäviö lähdössä C on merkityksetön.

Jos transistorin JA- tai transistorin NAND-portit tarvitsevat enemmän kuin kaksi tuloa, voidaan hyvinkin liittää useampia transistoreja esitetyissä malleissa kolmen, neljän jne. tulo-AND- tai NAND-portin aikaansaamiseksi.

Yksittäisten transistorien jännitehäviöiden kompensoimiseksi V+ tulisi kuitenkin nostaa vastaavasti.

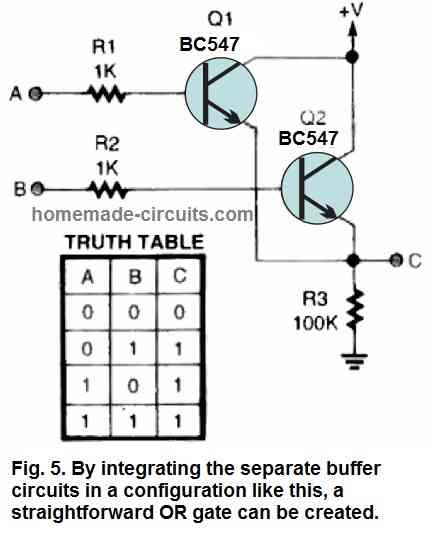

TAI portti käyttämällä kahta transistoria

Toinen logiikkapiirin muoto, jossa on kaksi tuloa, on nähtävissä kuvassa 5 yhdessä TAI-porttipiirin totuustaulukon kanssa.

Piirin lähtö on korkea, kun joko tulo A tai tulo B työnnetään korkealle, mutta peräkkäisistä transistoreista johtuen jännitehäviö on yli 0,5 volttia. Jälleen kerran näytetyt luvut osoittavat, että jännite ja virta on tarpeeksi seuraavan transistoriportin käyttämiseen.

NOR-portti käyttäen kahta transistoria

Kuva 6 kuvaa listamme seuraavaa porttia, kaksituloista NOR-porttia yhdessä sen totuustaulukon kanssa. Samalla tavalla kuin JA- ja NAND-portit reagoivat toisiinsa, TAI- ja NOR-piirit tekevät samoin.

Jokainen näytetyistä porteista pystyy syöttämään riittävästi vetoa ainakin yhden tai useamman vierekkäisen transistoriportin aktivoimiseksi.

Transistorilogiikkaporttisovellukset

Mitä teet yllä selitetyillä digitaalisilla piireillä, jotka sinulla nyt on? Mitä tahansa, mitä voit saavuttaa perinteisillä TTL- tai CMOS-porteilla, mutta ilman huolta syöttöjänniterajoituksista. Tässä on muutamia transistorilogiikan porttien sovelluksia toiminnassa.

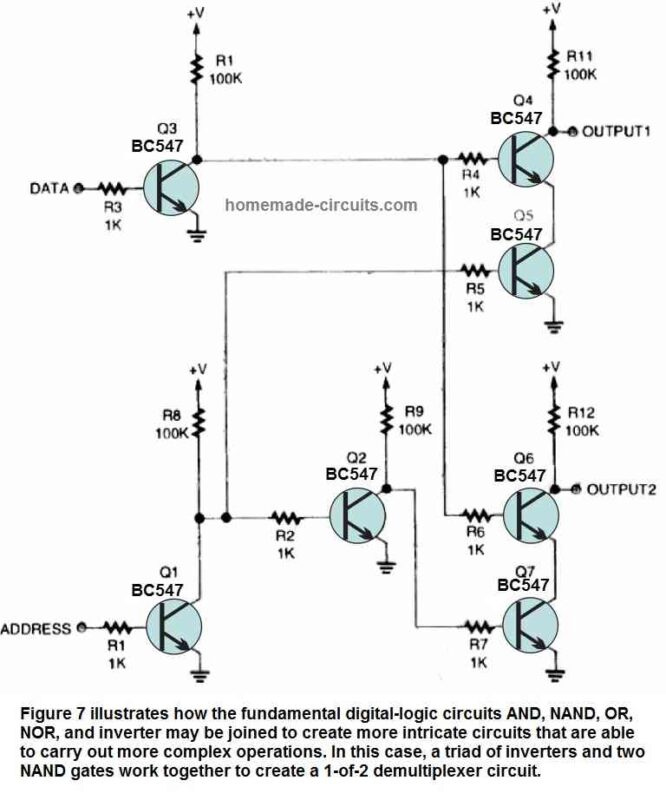

Demultiplekserin piiri

Kuvassa 7 näkyy 1/2-demultiplekseri, jossa on kolme NOT-porttia ja kaksi NAND-piiriä. Sopiva lähtö valitaan käyttämällä yksibittistä 'osoitetuloa', joka voi olla joko OUTPUT1 tai OUTPUT2, kun ajotietoja käytetään piiriin DATA-tulon avulla.

Piiri toimii tehokkaimmin, kun tiedonsiirtonopeus pidetään alle 10 kHz. Piirin toiminnallisuus on yksinkertainen. DATA-tuloon syötetään tarvittava signaali, joka kytkee Q3:n PÄÄLLE ja invertoi Q3:n kollektorissa tulevan datan.

Q1:n lähtö ohjataan korkeaksi, jos ADDRESS-tulo on matala (maadoitettu tai signaalia ei anneta). Q1:n kollektorissa korkea teho on jaettu kahteen polkuun. Ensimmäisellä polulla Q1:n lähtö syötetään Q5:n tukiasemaan (yksi kaksituloisen NAND-portin haaroista), mikä kytkee sen päälle ja siten 'aktivoi' Q4:stä ja Q5:stä koostuvan NAND-portin.

Toisella polulla Q1:n korkea lähtö syötetään samanaikaisesti toisen NOT-portin (Q2) tuloon. Kaksinkertaisen inversion jälkeen Q2:n teho laskee alhaiseksi. Tämä matala syötetään Q7:n tukiasemaan (toisen NAND-portin yksi napa, joka koostuu Q6:sta ja Q7:stä), jolloin NAND-piiri kytkeytyy pois päältä.

Kaikki DATA-tuloon syötetyt tiedot tai signaalit saapuvat OUTPUT1:een näissä olosuhteissa. Vaihtoehtoisesti tilanne on päinvastainen, jos ADDRESS-tuloon annetaan korkea signaali. Tämä tarkoittaa, että kaikki piirille toimitetut tiedot näkyvät OUTPUT2:ssa, koska Q4/Q5 NAND-portti on poistettu käytöstä ja Q6/Q7 NAND-portti on käytössä.

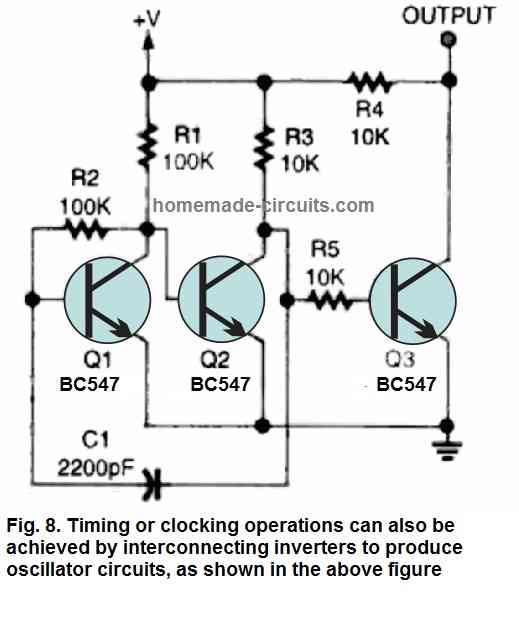

Oskillaattoripiiri (kellogeneraattori)

Seuraava transistorilogiikkaporttisovelluksemme, joka on kuvattu kuvassa 8, on peruskellogeneraattori (tunnetaan myös nimellä oskillaattori), joka koostuu kolmesta tavallisesta NOT-gate-invertteristä (joista yksi on biasoitu takaisinkytkentävastuksen R2 avulla, joka asettaa sen analoginen alue).

Lähdön tasaamiseksi on mukana kolmas NOT-portti (Q3), joka toimittaa komplementin oskillaattorin ulostuloon. C1-arvoa voidaan suurentaa tai pienentää piirin toimintataajuuden muuttamiseksi. Lähtöaaltomuodon taajuus on noin 7 kHz V+:lla 1,5 voltin tasajännitteellä, kun käytetään ilmoitettuja komponenttiarvoja.

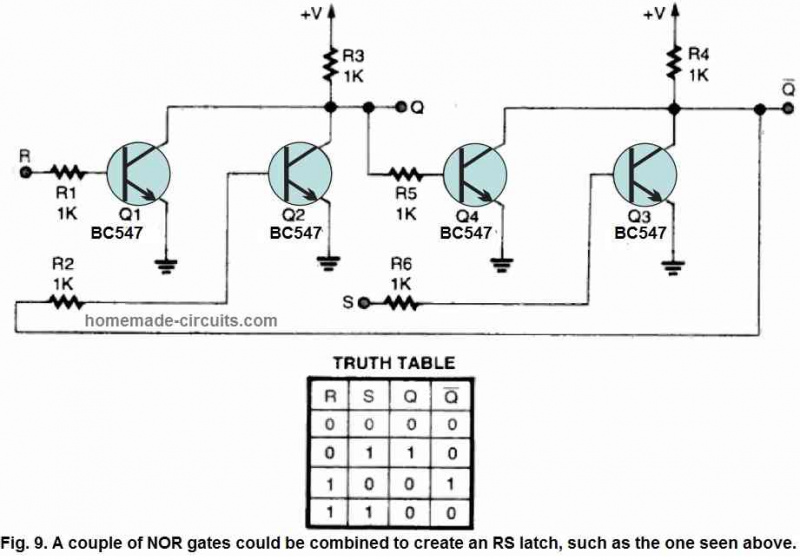

RS-salpapiiri

Kuva 9 esittää lopullista sovelluspiiriämme, RS-salpaa, joka koostuu kahdesta NOR-portista. Terveen lähtökäytön varmistamiseksi Q- ja Q-ulostuloissa vastukset R3 ja R4 on säädetty 1k ohmiin.

RS-salvan totuustaulukko näkyy kaavion rinnalla. Nämä ovat vain muutamia esimerkkejä useista luotettavista pienjännitteisistä digitaalisista logiikkaporttipiireistä, jotka voidaan luoda käyttämällä yksittäisiä transistoreja.

Transistorisoitua logiikkaa käyttävät piirit tarvitsevat liian monta osaa

Monet ongelmat voidaan ratkaista käyttämällä kaikkia näitä pienjännitetransistorisoituja logiikkapiirejä. Liian monien transistorisoitujen porttien käyttö voi kuitenkin johtaa uusiin ongelmiin.

Transistorien ja vastusten määrä voi kasvaa melko suureksi, jos rakentamassasi sovelluksessa on suuri määrä portteja, jotka vievät arvokasta tilaa.

Yksi tapa ratkaista tämä ongelma on käyttää transistoriryhmiä (monet transistorit muovissa) ja SIP (Single Inline Package) -vastuksia yksittäisten yksiköiden sijasta.

Yllä oleva lähestymistapa voi säästää tonnin tilaa piirilevyllä ja säilyttää samalla suorituskyvyn täysikokoisten vastaaviensa kanssa. Transistoriryhmiä tarjotaan pinta-asennettavissa, 14-nastaisessa läpireiässä ja nelipakkauksessa.

Useimmissa piireissä transistorityyppien sekoitus voi olla melko hyväksyttävää.

Siitä huolimatta on suositeltavaa, että kokeilija työskentelee yhden tyyppisen transistorin kanssa rakentaakseen transistorisoituja logiikkapiirejä (eli jos luot osan portista BC547:llä, yritä sitten käyttää samaa BJT:tä myös muiden jäljellä olevien porttien tekemiseen).

Syynä on se, että eri transistorimuunnelmilla voi olla hieman erilaisia ominaisuuksia ja ne voivat siten käyttäytyä eri tavalla.

Esimerkiksi joillekin transistoreille peruskytkentäraja voi olla suurempi tai pienempi kuin toisella, tai jollakin voi olla kokonaisvirran vahvistus, joka on hieman suurempi tai pienempi.

Toisaalta yksittäisen transistorin bulkkilaatikon ostamisen kustannukset voivat olla myös alhaisemmat. Piiriesi suorituskyky paranee, jos logiikkaporttisi on rakennettu käyttämällä yhteensopivia transistoreja, ja projekti kokonaisuudessaan on lopulta palkitsevampi.