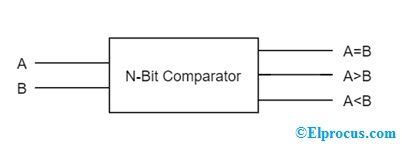

Kombinaatiopiireissä eri logiikkaportteja käytetään kooderin, multiplekserin, dekooderin ja multiplekserin purkamiseen. Näillä piireillä on joitain ominaisuuksia, kuten tämän piirin lähtö riippuu pääasiassa tasoista, jotka ovat tuloliittimissä milloin tahansa. Tämä piiri ei sisällä muistia. Tulon aikaisemmalla tilalla ei ole mitään vaikutusta tämän piirin nykyiseen tilaan. Yhdistelmäpiirin tulot ja lähdöt ovat n. syötteistä & ’m’ ei. lähdöt. Jotkut yhdistelmäpiireistä ovat puoli- ja täysi summain, vähennyslaskuri, kooderi, dekooderi, multiplekseri ja demultiplekseri. Tässä artikkelissa käsitellään yleiskatsausta puoli- ja täydestä summaimesta ja se toimii totuustaulukoiden kanssa.

Mikä on summain?

Summaja on a digitaalinen logiikkapiiri elektroniikassa, jota käytetään laajasti numeroiden lisäämiseen. Monissa tietokoneissa ja muun tyyppisissä prosessoreissa summaimia käytetään jopa osoitteiden ja niihin liittyvien toimintojen laskemiseen ja taulukkoindeksien laskemiseen ALU: ssa ja niitä käytetään jopa prosessorien muissa osissa. Ne voidaan rakentaa monille numeerisille esityksille, kuten ylimääräinen 3 tai binäärikoodattu desimaali. Lisäaineet luokitellaan periaatteessa kahteen tyyppiin: Half Adder ja Full Adder.

Mikä on puoliyksikkö ja täysi summainpiiri?

Puolisummutuspiirissä on kaksi tuloa: A ja B, jotka lisäävät kaksi sisääntuloa ja muodostavat siirron ja summan. Täydellä summainpiirillä on kolme tuloa: A ja C, jotka lisäävät kolme tulolukua ja tuottavat siirron ja summan. Tämä artikkeli antaa yksityiskohtaista tietoa puolisumman tarkoituksesta ja täysi summain taulukkomuodossa ja jopa piirikaavioissa. On jo mainittu, että lisäysten tärkein ja ratkaiseva tarkoitus on lisäys. Alla on yksityiskohtaiset tiedot puoli summaimen ja täyden summaimen teoria.

Peruslisäosa ja Täysi summain

Puolikas summaaja

Joten, tullessaan puolisumman skenaarioon, se lisää kaksi binäärilukua, joissa tulobittejä kutsutaan korotuksiksi ja lisäyksiksi ja tulokseksi tulee kaksi lähtöä, toinen on summa ja toinen on kantoaalto. Summaoperaation suorittamiseksi XOR syötetään molempiin tuloihin ja AND-portti lisätään molempiin tuloihin siirtojen tuottamiseksi.

HA: n toiminnallinen kaavio

Täydellisessä summainpiirissä se lisää 3 yksibittistä numeroa, joissa kahteen kolmesta bitistä voidaan viitata operandeina ja toiseen nimeltään bitteinä. Tuotettu tuotos on 2-bittinen lähtö ja näihin voidaan viitata to output carry ja sum.

Puolisumman avulla voit suunnitella yksinkertaisen lisäyksen logiikkaporttien avulla.

Katsotaanpa esimerkki kahden yksittäisen bitin lisäämisestä.

2-bittinen puolitiedot totuustaulukko on seuraava:

Puolitiedot totuustaulukko

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Nämä ovat vähiten mahdollisia yhden bitin yhdistelmiä. Mutta 1 + 1: n tulos on 10, summatulos on kirjoitettava uudelleen 2-bittisenä lähtöön. Täten yhtälöt voidaan kirjoittaa muodossa

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Tulos '1' / 10: stä on suoritus. ”SUM” on normaali lähtö ja ”CARRY” on suoritus.

Nyt on selvitetty, että 1-bittinen summain voidaan helposti toteuttaa XOR-portin avulla tuotokselle ”SUM” ja AND-portille ”kantoaallolle”.

Esimerkiksi, kun meidän on lisättävä kaksi 8-bittistä tavua yhteen, se voidaan toteuttaa käyttämällä täyden summaimen logiikkapiiriä. Puolisummain on hyödyllinen, kun haluat lisätä yhden binäärimerkkimäärän.

Tapa kehittää kahden binäärinumeron lisäyksiä olisi tehdä totuustaulukko ja vähentää sitä. Kun haluat tehdä kolminumeroisen summaimen, summaimen lisäysoperaatio suoritetaan kahdesti. Samalla tavalla, kun päätät tehdä nelinumeroisen summaimen, toiminto suoritetaan vielä kerran. Tämän teorian avulla oli selvää, että toteutus on yksinkertaista, mutta kehitys on aikaa vievä prosessi.

Yksinkertaisin lauseke käyttää yksinomaista TAI-toimintoa:

Summa = A XOR B

Kanna = A JA B

HA-looginen kaavio

Ja vastaava lauseke perus AND, OR ja NOT: n suhteen on:

SUMMA = A.B + A.B ’

VHDL-koodi puoliksi täyteen

Entiteetti ha on

Portti (a: STD_LOGIC

b: STD_LOGICissa

sha: ulos STD_LOGIC

cha: ulos STD_LOGIC)

loppu ha

Arkkitehtuuri Yllä olevan piirin käyttäytyminen on

alkaa

sha<= a xor b

ei<= a and b

loppukäyttäytyminen

Puoliyksikön IC-numero

Puolisumman toteutus voidaan suorittaa nopeilla CMOS-digitaaliloogisilla integroiduilla piireillä, kuten 74HCxx-sarja, joka sisältää SN74HC08 (7408) ja SN74HC86 (7486).

Puolen summaimen rajoitukset

Tärkein syy sille, että kutsutaan näitä binaarisia lisäaineita, kuten Half Adders, on, että ei ole aluetta sisällyttää siirtobitti aikaisempaan bittiin. Joten tämä on HA: n päärajoitus, jota käytetään kerran binaarisen summaimen tavoin, erityisesti reaaliaikaisissa tilanteissa, joihin liittyy useita bittejä. Joten tämä rajoitus voidaan voittaa käyttämällä täydellisiä summaimia.

Täysi summaaja

Tätä summainta on vaikea toteuttaa verrattuna puolisummaimeen.

Täydellinen summaimen toiminnallinen kaavio

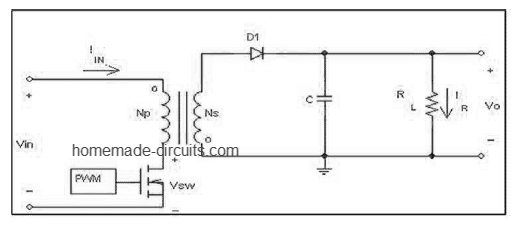

Puolisumman ja täyden summaimen välinen ero on siinä, että täydellä summaimella on kolme tuloa ja kaksi lähtöä, kun taas puolella summaimella on vain kaksi tuloa ja kaksi lähtöä. Kaksi ensimmäistä tuloa ovat A ja B ja kolmas tulo on C-IN-tuloliitäntä. Kun täysi summaimen logiikka on suunniteltu, merkitään kahdeksan niistä yhteen luomaan tavun laajuinen summain ja kaskadoidaan kantobitti yhdestä summaimesta toiseen.

FA-totuustaulukko

Lähdön kuljettaminen on merkitty C-OUT: ksi ja normaali lähtö on esitetty S: ksi, joka on ”SUM”.

Edellä esitetyllä tavalla täysi summajan totuus-taulukko , täyden summaimen piirin toteutus voidaan ymmärtää helposti. SUM ’S’ tuotetaan kahdessa vaiheessa:

- XOR: lla toimitetut tulot ”A” ja “B”

- A XOR B: n tulos Xoroidaan sitten C-IN: llä

Tämä tuottaa summan ja C-OUT on totta vain, kun jompikumpi kolmesta tulosta on KORKEA, C-OUT on KORKEA. Joten voimme toteuttaa täydellisen summainpiirin kahden puolisummutuspiirin avulla. Aluksi puolisummainta käytetään lisäämään A ja B osittaisen summan tuottamiseksi ja toisen puoliskon summaimen logiikkaa voidaan käyttää lisäämään C-IN ensimmäisen puoliskon summaimen tuottamaan summaan lopullisen S-tuloksen saamiseksi.

Jos jokin puolisummajan logiikasta tuottaa kantoa, tulee lähtösiirtymä. Joten C-OUT on TAI-funktio puoli-summaimen Carry-lähdöille. Katsokaa alla olevan täyden summaimen piirin toteutusta.

Täydellinen summaimen looginen kaavio

Suurempien logiikkakaavioiden toteutus on mahdollista yllä olevan täyden summaimen logiikan avulla, yksinkertaisempaa symbolia käytetään useimmiten operaation esittämiseen. Alla on yksinkertaisempi kaavamainen esitys yhden bitin täydestä summaimesta.

Tämän tyyppisillä symboleilla voimme lisätä kaksi bittiä yhteen ottamalla siirron seuraavasta alemmasta suuruusluokasta ja lähettämällä siirron seuraavaan suurempaan suuruusluokkaan. Tietokoneessa monibittistä toimintaa varten jokainen bitti on esitettävä täydellä summaimella ja lisättävä samanaikaisesti. Siten kahden 8-bittisen numeron lisäämiseen tarvitaan 8 täyttä summainta, jotka voidaan muodostaa kasaamalla kaksi 4-bittisestä lohkosta.

Puolet täysi ja täysi summa K-Mapin avulla

Jopa summa- ja suoritusarvot puoli-summaimelle voidaan saada myös Karnaugh-kartan (K-kartta) menetelmällä. puoli summain ja täysi summain totuusarvoinen lauseke voidaan saada K-kartan kautta. Joten näiden summaajien K-karttaa käsitellään jäljempänä.

Puolisumman K-kartta on

HA K-kartta

Täydellinen summain K-Map on

FA K-kartta

SUM: n ja Carryn looginen ilmaisu

Summan (S) looginen lauseke voidaan määrittää taulukossa mainittujen syötteiden perusteella.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A’B ’+ AB) + Cin’ (A’B + A B ’)

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

Siirron (Cout) looginen lauseke voidaan määrittää taulukossa mainittujen syötteiden perusteella.

= A’B Cin + AB’Cin + AB Cin ’+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

Edellä mainittujen totuustaulukoiden avulla voidaan saada tulokset ja menettely on:

Yhdistelmäpiiri yhdistää piirin eri portit, joissa ne voivat olla kooderi, dekooderi, multiplekseri ja demultiplekseri . Yhdistelmäpiirien ominaisuudet ovat seuraavat.

- Lähtö milloin tahansa ajankohtana perustuu vain tuloliittimissä oleviin tasoihin.

- Se ei käytä muistia. Aikaisemmalla tulotilalla ei ole mitään vaikutusta piirin nykyiseen tilaan.

- Sillä voi olla mikä tahansa määrä tuloja ja m lähtöä.

VHDL-koodaus

VHDL-koodaus täydelle summaimelle Sisällytä seuraavat.

kokonaisuus_add on

Portti (a: STD_LOGIC

b: STD_LOGICissa

cin: julkaisussa STD_LOGIC

summa: ulos STD_LOGIC

cout: ulos STD_LOGIC)

end full_add

Arkkitehtuuri full_add: n käyttäytyminen on

komponentti ha on

Portti (a: STD_LOGIC

b: STD_LOGICissa

sha: ulos STD_LOGIC

cha: ulos STD_LOGIC)

loppukomponentti

signaali s_s, c1, c2: STD_LOGIC

alkaa

HA1: ha-satamakartta (a, b, s_s, c1)

HA2: ha-satamakartta (s_s, cin, summa, c2)

kustannus<=c1 or c2

loppukäyttäytyminen

puoli- ja täyden summaimen välinen ero on, että puoli summain tuottaa tuloksia ja täysi summain käyttää puoli summain jonkin muun tuloksen tuottamiseen. Samalla tavalla, kun Täysi-summain koostuu kahdesta Puolisummasta, Täysi-summain on todellinen lohko, jota käytämme aritmeettisten piirien luomiseen.

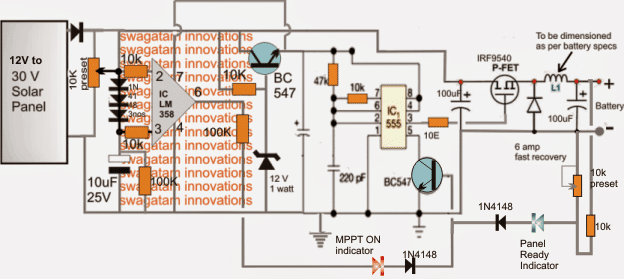

Kuljeta Lookahead-lisäosia

Ripple carry -lisäpiirien käsitteessä lisäykseen tarvittavat bitit ovat heti saatavilla. Jokaisella summaimen osalla on oltava aikaa kuljettamisen saapumiselle edellisestä summaimesta. Tämän vuoksi SUM: n ja CARRY: n tuottaminen vie enemmän aikaa, kun piirin kukin osa odottaa tulon saapumista.

Esimerkiksi ulostulon toimittamiseksi n: nnelle lohkolle sen on vastaanotettava tulo (n-1): stä lohkosta. Ja tätä viivettä kutsutaan vastaavasti etenemisviiveeksi.

Aaltoilun kantaja-summaimen viiveen voittamiseksi otettiin käyttöön kannettava-lookahead-summain. Tässä käyttämällä monimutkaista laitteistoa etenemisviive voidaan minimoida. Alla olevassa kaaviossa on esitetty kannettava-lookahead-summain, joka käyttää täydellisiä lisäaineita.

Carry Lookahead käyttämällä täyttä summainta

Totuustaulukko ja vastaavat lähtöyhtälöt ovat

| TO | B | C | C + 1 | Kunto |

| 0 | 0 | 0 | 0 | Ei kantoa Tuottaa |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | Ei kantoa Lisääntyä |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Kanna Tuottaa |

| 1 | 1 | 1 | 1 |

Kuljetuksen etenemisyhtälö on Pi = Ai XOR Bi ja kantogeneraattori on Gi = Ai * Bi. Näillä yhtälöillä summa- ja kantoyhtälöt voidaan esittää muodossa

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi toimittaa kantoa vain, kun sekä tulot Ai että Bi ovat 1 ottamatta huomioon tulonsiirtoa. Pi liittyy kuljettamisen etenemiseen Ci: stä Ci + 1: een.

Half-summaimen ja täyden summaimen välinen ero

ero puoli- ja täyden summaimen taulukon välillä näkyy alla.

| Puolikas summaaja | Täysi summaaja |

| Half Adder (HA) on yhdistelmälogiikkapiiri ja tätä piiriä käytetään lisäämään kaksi yksibittistä numeroa. | Full Adder (FA) on yhdistelmäpiiri ja tätä virtapiiriä käytetään lisäämään kolme yhden bitin numeroa. |

| HA: ssa ei voida lisätä seuraavaan vaiheeseen, kun edellinen lisäys on muodostettu. | FA: ssa, kun siirto on muodostettu aikaisemmasta lisäyksestä, se voidaan lisätä seuraavaan vaiheeseen. |

| Puolikas summain sisältää kaksi loogista porttia, kuten AND-portti ja EX-OR-portti. | Täysi summain sisältää kaksi EX-OR-porttia, kaksi OR-porttia ja kaksi AND-porttia. |

| Puolisumman tulobitit ovat kaksi kuten A, B. | Täyden summaimen tulobitit ovat kolme, kuten A, B & C-sisääntulo |

| Puolet summaimen summa- ja kantoyhtälö on S = a⊕b C = a * b | Täydellinen summaimen looginen lauseke on S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA: ta käytetään tietokoneissa, laskimissa, digitaalisessa mittauksessa käytettävissä laitteissa jne. | FA: ta käytetään digitaalisissa prosessoreissa, monibittisissä lisäyksissä jne. |

keskeiset erot puoli- ja täydellisen summaimen välillä käsitellään jäljempänä.

- Puoli summain tuottaa summan ja kanteen lisäämällä kaksi binäärituloa, kun taas täyttä summainta käytetään summan ja siirron tuottamiseen lisäämällä kolme binäärituloa. Sekä puoli- että täysi summainlaitteistoarkkitehtuuri eivät ole samat.

- Tärkein piirre, joka erottaa HA: n ja FA: n, on se, että HA: ssa ei ole sellaista sopimusta, joka ottaisi huomioon viimeisen lisäyksen kantamisen kuten sen syöttö. Mutta FA etsii tietyn syötesarakkeen, kuten Cin, viimeisen lisäyksen siirtobitin huomioon ottamiseksi.

- Nämä kaksi lisäystä osoittavat eron piirin rakenteeseen käytettyjen komponenttien perusteella. Puoliominaisuudet (HA: t) on suunniteltu kahden logiikkaportin, kuten AND & EX-OR, yhdistelmällä, kun taas FA on suunniteltu kolmen AND: n, kahden XOR: n ja yhden OR-portin yhdistelmällä.

- Pohjimmiltaan HA: t toimivat kahdella kahdella 1-bittisellä tulolla, kun taas FA: t toimivat kolmella 1-bittisellä tulolla. Puoli summainta käytetään erilaisissa elektronisissa laitteissa lisäyksen arvioimiseksi, kun taas täyttä summainta käytetään digitaalisissa prosessoreissa pitkän bitin lisäämiseen.

- Näiden kahden summaimen yhtäläisyydet ovat, että molemmat HA ja FA ovat yhdistelmä digitaalisia piirejä, joten ne eivät käytä mitään muistielementtejä, kuten peräkkäisiä piirejä. Nämä piirit ovat välttämättömiä aritmeettiselle toiminnalle binääriluvun lisäyksen aikaansaamiseksi.

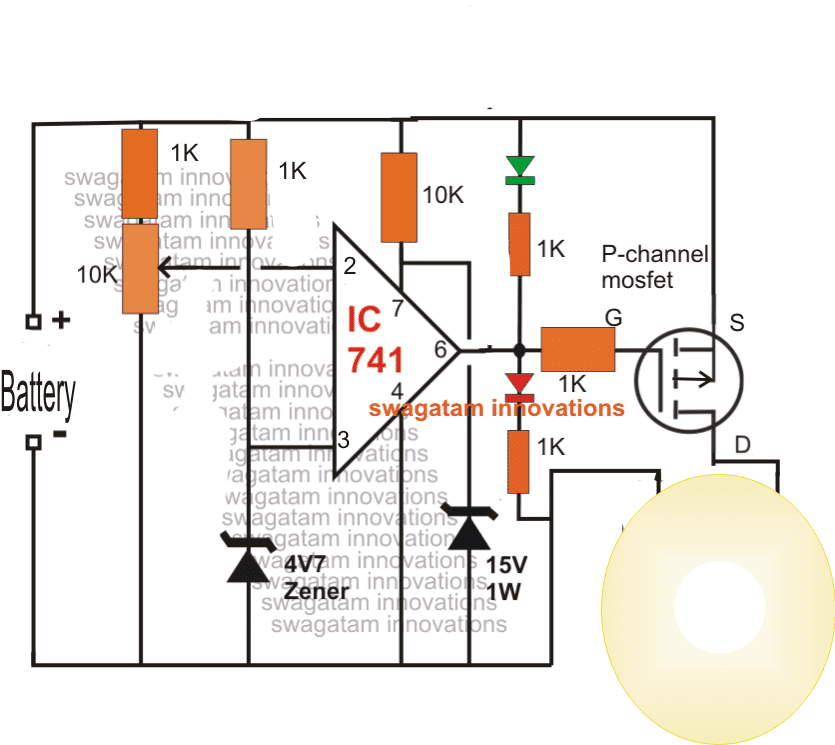

Täydellinen summaimen toteutus puolisummien avulla

FA: n toteutus voidaan tehdä kahden loogisesti yhdistetyn puolikaslisälaitteen kautta. Tämän lohkokaavio voidaan näyttää alla, joka kertoo FA: n yhteyden kahdella puolisummaisella.

Aikaisempien laskelmien summa ja kantoyhtälöt ovat

S = A ’B’ Cin + A ’BC’ + ABCinissä

Cout = AB + ACin + BCin

Summayhtälö voidaan kirjoittaa seuraavasti.

Cin (A’B ’+ AB) + C’ (A‘B + A B ’)

Joten summa = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C’in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

Cout voidaan kirjoittaa seuraavasti.

COUT = AB + ACin + BCin.

Cout = AB + + pettymyksiä BCIN (A + A)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ’B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ’) + A’ B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ’B Cin

= AB + AB ’Cin + A’ B Cin

= AB + Cin (AB ’+ A’B)

Siksi COUT = AB + Cin (A EX-OR B)

Edellä olevista kahdesta summasta & kantoyhtälöstä riippuen FA-piiri voidaan toteuttaa kahden HA: n ja OR-portin avulla. Piirikaavio täydestä summaimesta, jossa on kaksi puolisummaa, on esitetty yllä.

Täysi summain, joka käyttää kahta puolivälissä olevaa summainta

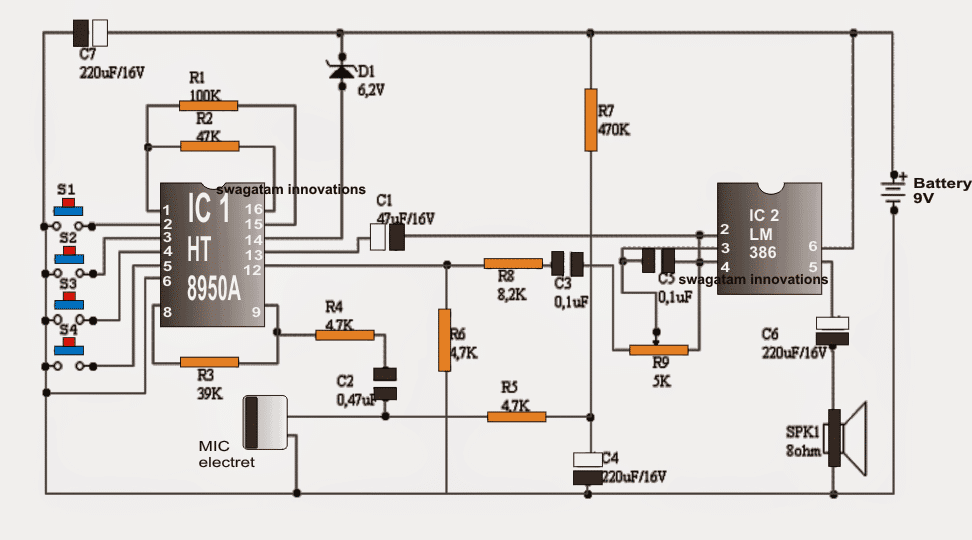

Täysi Adder-suunnittelu NAND-porttien avulla

NAND-portti on eräänlainen universaaliportti, jota käytetään kaikenlaisen logiikkasuunnittelun toteuttamiseen. FA-piiri NAND-porttikaavion kanssa on esitetty alla.

FA käyttäen NAND Gatesia

FA on helppo yhden bittinen summain, ja jos haluamme suorittaa n-bittisen lisäyksen, niin n ei. yhden bitin FA: ta on käytettävä kaskadiyhteysmuodossa.

Edut

puoli- ja täyden summaimen edut Sisällytä seuraavat.

- Puoli-summaimen tärkein tarkoitus on lisätä kaksi yksibittistä numeroa

- Täydellisillä summaimilla on mahdollisuus lisätä siirtobitti, joka on seurausta edellisestä lisäyksestä

- Täydellä summaimella voidaan toteuttaa ratkaisevia piirejä, kuten summain, multiplekseri ja monet muut

- Täydelliset summainpiirit kuluttavat vähän virtaa

- Täydellisen summaimen edut puoleen summaimeen verrattuna ovat, että täyttä summainta käytetään puoli-summaimen haittapuolen voittamiseen, koska puolisummainta käytetään pääasiassa kahden 1-bittisen numeron lisäämiseen. Puolet lisäyksistä eivät lisää kantokärkeä, joten tämän täydellisen summaimen voittamiseksi käytetään. Täydellisessä summaimessa voidaan lisätä kolme bittiä ja tuottaa kaksi lähtöä.

- Lisäaineiden suunnittelu on yksinkertaista ja se on peruselementti, jotta yhden bittinen lisäys voidaan helposti ymmärtää.

- Tämä summain voidaan muuntaa puoliksi vähennyslaskijaksi lisäämällä invertteri.

- Käyttämällä täyttä summainta voidaan saavuttaa korkea teho.

- Suuri nopeus

- Erittäin voimakas syöttöjännitteen skaalaukseen

Haitat

puoli- ja täydellisen summaimen haitat Sisällytä seuraavat.

- Lisäksi puolisummeria ei voi käyttää ennen kantamista, joten sitä ei voida soveltaa monibittisen lisäyksen kaskadointiin.

- Tämän haitan voittamiseksi FA on tarpeen lisätä kolme 1 bittiä.

- Kun FA: ta käytetään ketjun muodossa, kuten RA (Ripple Adder), tällöin voidaan vähentää lähtötehoa.

Sovellukset

Puoli- ja täysi-summaimen sovellukset sisältävät seuraavat.

- Binaaribittien lisäys voidaan tehdä puoliksi summaimella käyttämällä tietokoneen ALU: ta, koska se käyttää summainta.

- Puolisummeriyhdistelmää voidaan käyttää täyden summainpiirin suunnitteluun.

- Puolet summaimista käytetään laskimissa ja osoitteiden sekä taulukoiden mittaamiseen

- Näitä piirejä käytetään käsittelemään erilaisia sovelluksia digitaalisissa piireissä. Tulevaisuudessa sillä on keskeinen rooli digitaalisessa elektroniikassa.

- FA-piiriä käytetään elementtinä monissa suurissa piireissä, kuten Ripple Carry Adder. Tämä summain lisää bittien määrän samanaikaisesti.

- FA: ita käytetään aritmeettisessa logiikkayksikössä (ALU)

- FA: ita käytetään grafiikkaan liittyvissä sovelluksissa, kuten GPU (Graphics Processing Unit)

- Näitä käytetään kertolaskupiirissä suorittamaan kertokerroin.

- Tietokoneessa muistiosoitteen luomiseksi ja ohjelman vastapisteen rakentamiseksi seuraavaa käskyä varten käytetään aritmeettista logiikkayksikköä käyttämällä Täydellisiä lisäyksiä.

Siten aina, kun kahden binääriluvun lisäys suoritetaan, numerot lisätään ensin vähiten bittejä. Tämä prosessi voidaan suorittaa puolisumman kautta, koska yksinkertaisin n / w, joka sallii kahden 1-bittisen numeron lisäämisen. Tämän summaimen tulot ovat binaarisia numeroita, kun taas lähdöt ovat summa (S) ja siirto (C).

Aina kun numeroiden määrä sisältyy, HA-verkkoa käytetään yksinkertaisesti yhdistämään vähiten numeroita, koska HA ei voi lisätä aikaisemman luokan kantonumeroa. Täydellinen summain voidaan määritellä kaikkien digitaalisten aritmeettisten laitteiden perustaksi. Tätä käytetään lisäämään kolme yksinumeroista numeroa. Tämä summain sisältää kolme tuloa, kuten A, B ja Cin, kun taas lähdöt ovat Sum ja Cout.

Liittyvät käsitteet

puoli- ja täysi summaimeen liittyvät käsitteet vain ei pidä kiinni yhdestä tarkoituksesta. Niitä käytetään laajasti monissa sovelluksissa, ja mainitaan muutama asiaan liittyvä:

- Puoli summaimen ja täyden summaimen IC-numero

- 8-bittisen summaimen kehitys

- Mitkä ovat puolisumman varotoimet?

- JAVA Ripple Carry Adder -sovellus

Siksi tässä on kyse puoli summaimen ja täyden summaimen teoria yhdessä totuustaulukoiden ja logiikkakaavioiden kanssa näytetään myös täyden summaimen suunnittelu käyttämällä puolisummeripiiriä. Monet puoli summain ja täysi summa pdf saatavilla on asiakirjoja, jotka tarjoavat kattavaa tietoa näistä käsitteistä. Lisäksi on tärkeää tietää miten 4-bittinen täysi summain toteutetaan ?