JTAG (Joint Test Action Group) on vakiintunut IEEE 1149.1 -standardi, joka kehitettiin vuonna 1980 ratkaisemaan elektroniikkalevyissä tai -korteissa esiintyviä valmistusongelmia. painetut piirilevyt . Tätä tekniikkaa käytetään tarjoamaan riittävästi testipääsyä jokaiselle monimutkaiselle kortille, kun testipääsy on vähentynyt. Siten rajojen skannaustekniikka lanseerattiin & JTAG-standardi tai JTAG-spesifikaatio on perustettu. Elektroniikan monimutkaisuus on kasvanut päivä päivältä, joten JTAG-spesifikaatiosta on tullut hyväksytty testimuoto monimutkaisten ja kompaktien elektroniikkayksiköiden testaamiseen. Tässä artikkelissa käsitellään yleiskatsausta a JTAG protokolla – työskentely sovellusten kanssa.

Mikä on JTAG?

IEEE 1149.1 -standardin testipääsyportille ja Boundary-Scan Architecturelle annettu nimi tunnetaan nimellä JTAG (Joint Test Action Group). Tätä rajatarkistusarkkitehtuuria käytetään enimmäkseen tietokoneissa prosessorit koska Intel julkaisi ensimmäisen JTAG-prosessorin. Tämä IEEE-standardi yksinkertaisesti määrittelee, kuinka tietokoneen piirit testataan sen varmistamiseksi, toimiiko se oikein valmistusprosessin jälkeen. Piirilevyillä testataan juotosliitokset.

Joint Test Action Group tarjoaa testaajille pins-out-näkymän jokaisen IC-levyn kanssa, mikä auttaa tunnistamaan piirilevyn viat. Kun tämä protokolla on liitetty siruun, se voi liittää siruun anturin antamalla kehittäjän ohjata sirua sekä sen yhteyksiä muihin siruihin. Myös kehittäjät voivat käyttää Joint Test Action -ryhmän käyttöliittymää laiteohjelmiston kopioimiseen elektronisen laitteen haihtumattomaan muistiin.

Kokoonpano/Pin Out

Joint Test Action Group sisältää 20 nastaa, joista jokaista nastaa ja sen toimintoja käsitellään alla.

Pin1 (VTref): Tämä on kohteen referenssijännitteen nasta, jota käytetään liittämään kohteen päävirtalähteeseen, jonka jännite on 1,5–5,0 VDC.

Pin2 (Vsupply): Tämä on tavoitesyöttöjännite, jota käytetään 1,5 VDC – 5,0 VDC:n pääjännitelähteen kytkemiseen.

Pin3 (nTRST): Tämä on testipalautusnasta, jota käytetään TAP-ohjaimen tilakoneen nollaamiseen.

Nastat (4, 6, 8, 10, 12, 14, 16, 18 ja 20): Nämä ovat yleisiä GND-nastoja.

Pin5 (TDI): Tämä on testidata pinnissä. Nämä tiedot siirretään kohdelaitteeseen. Tämä tappi on vedettävä ylös määritetyssä tilassa kohdelevylle.

Pin7 (TMS): Tämä on testitilan tilanasta, joka vedetään määrittämään TAP-ohjaimen tilakoneen seuraava tila.

Pin9 (TCK): Tämä on testikellon nasta, joka synkronoi sisäiset tilakoneen toiminnot TAP-ohjaimessa.

Pin11 (RTCK): Tämä on Input Return TCK -nasta, jota käytetään adaptiivista kelloa tukevissa laitteissa.

Pin13 (TDO): Tämä on Test Data Out -nasta, joten tiedot siirretään kohdelaitteesta Flyswatteriin.

Pin15 (nSRST): Tämä on Target System Reset -nasta, joka on kytketty kohteen päänollaussignaaliin.

Nastat 17 ja 19 (NC): Nämä eivät ole kytkettyjä nastoja.

JTAG toimii

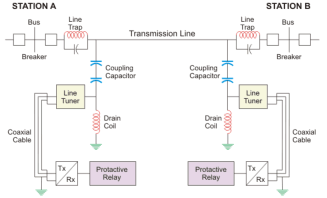

JTAG:n alkuperäinen käyttö on rajatestausta. Tässä on yksinkertainen piirilevy, joka sisältää kaksi IC:tä, kuten CPU & FPGA . Tyypillinen kortti voi sisältää useita IC:itä. Yleensä IC:t sisältävät monia nastoja, jotka on yhdistetty useiden liitäntöjen kanssa. Tässä, seuraavassa kaaviossa, on esitetty vain neljä liitäntää.

Joten jos suunnittelet monia levyjä, joissa jokaisella levyllä on tuhansia liitäntöjä. Siinä on huonoja levyjä. Joten meidän on tarkistettava, mikä kortti toimii ja mikä ei. Sitä varten suunniteltiin Joint Test Action Group.

Tämä protokolla voi käyttää kaikkien sirujen ohjausnastaa, mutta seuraavassa kaaviossa Joint Test Action Group tekee kaikki suorittimen lähtönastat ja kaikki FPGA:n tulonastat. Sen jälkeen lähettämällä jonkin verran dataa CPU:n nastoista ja lukemalla nastojen arvot FPGA:sta, JTAG toteaa, että piirilevyn liitännät ovat kunnossa.

Itse asiassa Joint Test Action Group sisältää neljä logiikkasignaalia TDI, TDO, TMS & TCK. Ja nämä signaalit on yhdistettävä tietyllä tavalla. Aluksi TMS & TCK on kytketty rinnan kaikkiin JTAG:n IC:ihin.

Sen jälkeen sekä TDI että TDO yhdistetään ketjun muodostamiseksi. Kuten voit huomata, jokainen JTAG-yhteensopiva IC sisältää 4-nastaa, joita käytetään JTAG:lle, jossa 3-nastaiset ovat tuloja ja 4. nasta on lähtönä. Viides nasta, kuten TRST, on valinnainen. Yleensä JTAG-nastoja ei jaeta muihin tarkoituksiin.

Joint Test Action Groupia käyttämällä kaikki IC:t käyttävät rajatestausta, jonka alkuperäinen syy on JTAG:n luoma. Tällä hetkellä tämän protokollan käyttöä on laajennettu mahdollistamaan erilaisia asioita, kuten FPGA:iden määrittäminen, ja sen jälkeen JTAGia käytetään FPGA-ytimessä virheenkorjaustarkoituksiin.

JTAG-arkkitehtuuri

JTAG-arkkitehtuuri näkyy alla. Tässä arkkitehtuurissa kaikki signaalit laitteen ydinlogiikan ja nastojen välillä keskeytetään sarjaskannauspolun kautta, jota kutsutaan BSR- tai Boundary Scan Registeriksi. Tämä BSR sisältää erilaisia rajapyyhkäisy 'soluja'. Yleensä nämä rajapyyhkäisysolut eivät ole näkyvissä, mutta niiden avulla voidaan asettaa tai lukea arvoja testitilassa laitteen nastoista.

JTAG-liitäntä, jota kutsutaan TAP- tai Test Access Portiksi, käyttää erilaisia signaaleja tukemaan rajapyyhkäisyä, kuten TCK, TMS, TDI, TDO ja TRST.

- TCK tai Test Clock -signaali yksinkertaisesti synkronoi tilakoneen sisäiset toiminnot.

- TMS- tai Test Mode Select -signaali näytteistetään testikellosignaalin kasvavassa reunassa seuraavan tilan päättämiseksi.

- TDI tai Test Data In -signaali merkitsee siirrettyä dataa testilaitteeseen muuten ohjelmointilogiikkaan. Kun sisätilakone on oikeassa tilassa, siitä otetaan näyte TCK:n kasvavasta reunasta.

- TDO tai Test Data Out -signaali tarkoittaa testilaitteen siirrettyä dataa, muuten ohjelmointilogiikkaa. Kun sisätilakone on oikeassa tilassa, se on voimassa TCK:n laskevalla reunalla

- TRST tai Test Reset on valinnainen nasta, jota käytetään TAP-ohjaimen tilakoneen nollaukseen.

TAP-ohjain

JTAG-arkkitehtuurin testiliityntäpiste koostuu TAP-ohjaimesta, käskyrekisteristä ja testidatarekistereistä. Tämä ohjain sisältää testaustilakoneen, joka on vastuussa TMS- ja TCK-signaalien lukemisesta. Tässä datan i/p-nastaa käytetään yksinkertaisesti lataamaan dataa rajasoluihin IC-ytimen ja fyysisten nastojen välissä, ja myös lataamaan dataa johonkin datarekistereistä tai käskyrekisteriin. Data o/p -nastaa käytetään tietojen lukemiseen joko rekistereistä tai rajasoluista.

TAP-ohjaimen tilakonetta ohjaa TMS ja se kellotetaan TCK:lla. Tilakone käyttää kahta polkua kahden eri tilan, kuten ohjetilan ja datatilan, merkitsemiseen.

Rekisterit

Rajaskannauksessa on saatavilla kahdenlaisia rekistereitä. Jokainen yhteensopiva laite sisältää vähintään kaksi datarekisteriä ja yhden käskyrekisterin.

Ohjerekisteri

Käskyrekisteriä käytetään nykyisen käskyn säilyttämiseen. Joten TAP-ohjain käyttää sen tietoja päättääkseen, mitä suoritetaan saaduilla signaaleilla. Useimmiten käskyrekisteritiedot kuvaavat, mihin tietorekistereistä signaalit on välitettävä.

Tietorekisterit

Tietorekistereistä on saatavilla kolme tyyppiä: BSR (Boundary Scan Register), BYPASS & ID CODES -rekisteri. Ja myös muita tietorekistereitä voi olla olemassa, mutta ne eivät ole välttämättömiä JTAG-standardin osana.

Boundary Scan Register (BSR)

BSR on tärkein testaustietorekisteri, jota käytetään tiedon siirtämiseen laitteen I/O-nastoista ja niiden välillä.

OHITTAA

Ohitus on yksibittinen rekisteri, jota käytetään tietojen välittämiseen TDI - TDO:sta. Siten se mahdollistaa piirin lisälaitteiden testaamisen vähimmäismäärällä.

ID KOODIT

Tämäntyyppinen tietorekisteri sisältää laitteen tunnuskoodin ja versionumeron. Joten nämä tiedot mahdollistavat laitteen yhdistämisen sen BSDL-tiedostoon (Boundary Scan Description Language). Tämä tiedosto sisälsi laitteen Boundary Scan -määritystiedot.

JTAG:n toiminta on alun perin se ohjetila, jossa valitaan yksi tämän tilan 'polun' tiloista, jolloin operaattori saa kelloa TDI:n käskyn sisällä. Sen jälkeen tilakone kehittyy, kunnes se järjestyy uudelleen. Useimpien ohjeiden seuraava vaihe on datatilan valitseminen. Joten tässä tilassa tiedot ladataan TDI:n kautta TDO:sta luettavaksi. TDI & TDO:ssa datapolut järjestetään kellotetun käskyn mukaisesti. Kun luku/kirjoitustoiminto on suoritettu, tilakone kehittyy jälleen nollaustilaan.

Ero JTAG Vs UART välillä

Ero JTAG:n ja UART:n välillä sisältää seuraavan.

| JTAG |

UART |

| Termi 'JTAG' tarkoittaa Joint Test Action Groupia. | Termi ' UART ” tarkoittaa Universal Asynchronous Receiver/Transmitter. |

| Se on synkroninen käyttöliittymä, joka käyttää sisäänrakennettua laitteistoa salaman ohjelmointiin . | UART on asynkroninen käyttöliittymä, joka käyttää käynnistyslatainta, joka toimii muistissa. |

| Se on joukko testiportteja, joita käytetään virheenkorjaukseen, mutta jota voidaan käyttää myös laiteohjelmiston ohjelmoimiseen (mitä yleensä tehdään).

|

UART on eräänlainen siru, joka ohjaa tiedonsiirtoa laitteelle, kuten mikro-ohjaimelle, ROM-muistille, RAM-muistille jne. Useimmiten se on sarjayhteys, jonka avulla voimme kommunikoida laitteen kanssa. |

| Näitä on saatavana neljänä tyyppinä TDI, TDO, TCK, TMS ja TRST. | Näitä on saatavana kahdentyyppisinä tyhminä UART- ja FIFO-UART-versioina. |

| Joint Test Action Group on sarjaohjelmointi- tai tiedonsaantiprotokolla, jota käytetään mikro-ohjainten ja niihin liittyvien laitteiden liitännässä. | UART on eräänlainen siru, muuten mikro-ohjaimen alikomponentti, jota käytetään tarjoamaan laitteisto asynkronisen sarjavirran, kuten RS-232/RS-485, luomiseen. |

| JTAG-komponentit ovat prosessorit, FPGA:t, CPLD:t , jne. | UART-komponentteja ovat CLK-generaattori, I/O-siirtorekisterit, lähetys- tai vastaanottopuskurit, järjestelmätietoväylän puskuri, luku- tai kirjoitusohjauslogiikka jne. |

JTAG Protocol Analyzer

JTAG-protokollaanalysaattori, kuten PGY-JTAG-EX-PD, on eräänlainen protokolla-analysaattori, joka sisältää joitain ominaisuuksia isännän ja testattavan suunnittelun välisen viestinnän sieppaamiseen ja virheenkorjaukseen. Tämän tyyppinen analysaattori on johtava instrumentti, jonka avulla testaus- ja suunnitteluinsinöörit voivat testata JTAG:n tiettyjä rakenteita sen spesifikaatioiden mukaisesti järjestämällä PGY-JTAG-EX-PD:n, kuten Master tai Slave, generoimaan JTAG-liikennettä ja dekoodaamaan JTAG-paketit. Joint Test Action Group -protokolla.

ominaisuudet

JTAG-protokollaanalysaattorin ominaisuuksia ovat seuraavat.

- Se tukee jopa 25MH JTAG-taajuuksia.

- Se luo JTAG-liikenteen ja protokollan dekoodauksen väylälle samanaikaisesti.

- Siinä on JTAG Master -ominaisuus.

- Muuttuvat JTAG-datanopeudet ja käyttösuhde.

- Käyttäjän määrittämät TDI- ja TCK-viiveet.

- Isäntätietokoneen USB 2.0 tai 3.0 liitäntä.

- Virheanalyysi protokollan purkamisessa

- Protokolladekoodattu väylän ajoituskaavio.

- Jatkuva protokollatietojen suoratoisto isäntätietokoneeseen suuren puskurin tarjoamiseksi.

- Protokollatoimintoluettelo.

- Eri nopeuksilla voidaan kirjoittaa harjoitusskripti useiden datakehysten generoinnin yhdistämiseksi.

Ajoituskaavio

The JTAGin ajoituskaavio protokolla näkyy alla. Seuraavassa kaaviossa TDO-nasta pysyy korkean impedanssin tilassa paitsi shift-IR/shift-DR-ohjaimen tilassa.

Shift-IR- ja Shift-DR-ohjaimen olosuhteissa TDO-nasta päivitetään TCK:n laskevassa reunassa Targetin kautta ja näytteistetään TCK:n kasvavassa reunassa isännän kautta.

Sekä TDI- että TMS-nastat otetaan yksinkertaisesti näytteiksi TCK:n kasvavasta reunasta Targetin kautta. Päivitetty laskevassa reunassa muuten TCK Hostin kautta.

Sovellukset

The JTAG-sovellukset Sisällytä seuraavat.

- Joint Test Action Groupia käytetään usein prosessoreissa antamaan pääsyoikeus niiden emulointi- tai virheenkorjaustoimintoihin.

- Kaikki CPLD:t ja FPGA:t käyttävät tätä käyttöliittymänä ohjelmointitoimintojensa käyttöön.

- Sitä käytetään PCB-testaukseen ilman fyysistä pääsyä

- Sitä käytetään levytason valmistustesteihin.

Tästä siis kaikesta on kyse yleiskatsaus JTAG:iin – pin-määritys, työskentely sovellusten kanssa. Alan standardia JTAG käytetään suunnittelun todentamiseen sekä PCB-testaukseen valmistuksen jälkeen. Tässä on kysymys sinulle, JTAG tarkoittaa?