Tärkein haittapuoli yhdistelmäpiiri eli se ei käytä muistia nykyisen ja edellisen tilan tallentamiseen. Siksi edellisellä tulotilalla ei ole mitään vaikutusta piirin nykyiseen tilaan. Sekä peräkkäisessä piirissä on muistia, joten lähtö voi vaihdella syötteen mukaan. Tämän tyyppiset piirit käyttävät edellistä tuloa, lähtöä, kelloa ja muistielementtiä. Tässä muistielementit voivat olla salpa tai varvastossut. Peräkkäiset piirit suunnitellaan erilaisilla menetelmillä, kuten käyttämällä ROM-levyjä ja läppää, PLA-levyjä, CPLD (monimutkainen ohjelmoitava logiikkalaite) , FPGA: t (kentän ohjelmoitava porttiryhmä) . Tässä artikkelissa aiomme keskustella vain siitä, kuinka suunnitella peräkkäinen piiri PLA: n avulla.

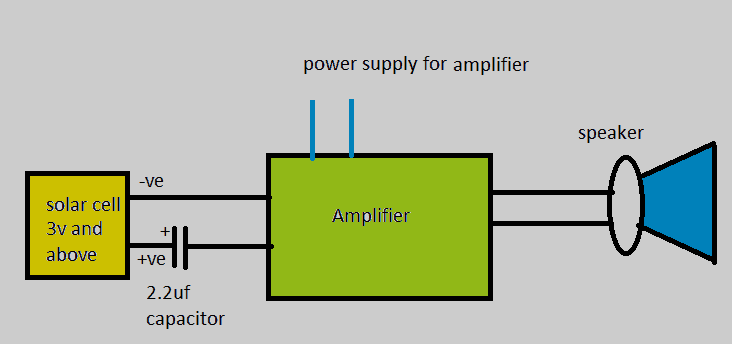

Peräkkäisen piirin lohkokaavio alla esitetyllä tavalla:

Peräkkäisen piirin lohkokaavio

Sarjapiirin suunnittelu PLA: n avulla

Peräkkäiset piirit voidaan toteuttaa PLA: illa (Programmable Logic Arrays) ja kiikkuilla. Tässä suunnittelussa tilan määritys voi olla tärkeä, koska hyvän tilan osoittamisen käyttö voi vähentää vaadittua tuotetermien määrää ja siten pienentää vaadittavaa PLA-kokoa. Tuotetermi, joka määritellään literaalien yhdistelmänä, jossa jokainen literaali on joko muuttuja tai sen negaatio.

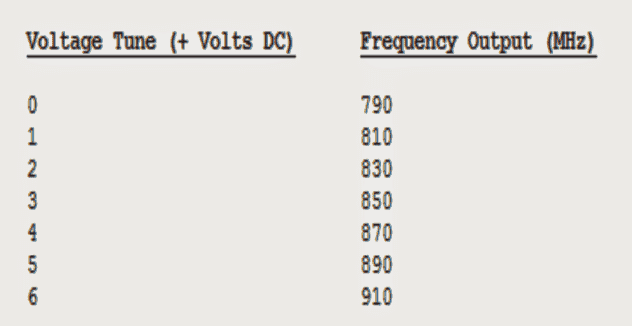

Katsotaanpa suunnittelun koodimuunnin. Seuraavassa taulukossa esitetty tilataulukko voidaan toteuttaa käyttämällä yhtä PLA: ta ja kolmea sandaalit kuvan osoittamalla tavalla. Tämä piirikokoonpano on hyvin samanlainen kuin ROM-kiikaripohjainen suunnittelu, paitsi että ROM korvataan sopivan kokoisella PLA: lla. Tilan määritys johtaa alla annettuun totuustaulukkoon. Tämä taulukko voitaisiin tallentaa PLA: han, jossa on neljä tuloa, 13 tuotetermiä ja neljä ulostuloa, mutta tämä tarjoaisi vähän pienemmän koon kuin 16 sanan ROM.

| X Q1 Q2 Q3 | Kanssa D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Taulukko: Totuustaulukko

ESITTÄÄ OSAVALTIO

| SEURAAVA VALTIO X = 0 1 | ESITTÄÄ LÄHTÖ (Z) |

| TO | B C | 1 0 |

B C | D E Ja E | 1 0 0 1 |

D ON | HH H M | 0 1 1 0 |

H M | A A TO - | 0 1 1 - |

Taulukko: valtion taulukko

Sarjapiirien suunnittelu PLA: n avulla

Karnaugh Mapin johdetut tulo-lähtöyhtälöt

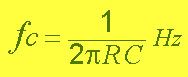

Tässä on seitsemän tilaa, tarvitaan kolme D-kiipeä. Siksi tarvitaan PLA-piiri, jossa on 4 tuloa ja 4 lähtöä. Jos otetaan huomioon koodimuuntimen tilan määritys, tuloksena oleva yhtälö ja D kiikun sisääntuloyhtälöt, jotka on johdettu Karnaugh'sta, voidaan kirjoittaa seuraavat yhtälöt

D1 = Q1 + = Q2 '

D2 = Q2 + = Q2 ”

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X Q3

| X Q1 Q2 Q3 | Kanssa D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 yksitoista

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Näitä yhtälöitä vastaava PLA-taulukko on annettu yllä olevassa taulukossa. Tämä taulukko voidaan toteuttaa käyttämällä PLA: ta, jossa on neljä tuloa, seitsemän tuotetermiä ja neljä lähtöä. Oletuksena on, että X = 0 ja Q1Q2Q3 = 000 tarkistaaksesi yllä olevan mallin toiminnan. Tämä valitsee rivit - - 0- ja 0 - - -0 taulukosta, joten Z = 0 ja D1D2D3 = 100. Aktiivisen kellon reunan jälkeen Q1Q2Q3 = 100. Jos seuraava tulo on X = 1, valitaan rivit - - 0 - ja - 1-, joten Z = 0 ja D1D2D3 = 110. Aktiivisen kellon reunan jälkeen Q1Q2Q3 = 110.

Ohjelmoitava logiikkaryhmä (PLA)

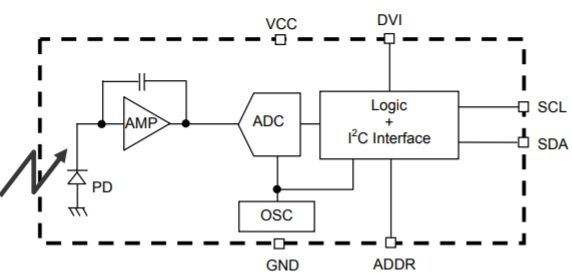

Ohjelmoitava logiikkataulukko on ohjelmoitava looginen laite. Sitä käytetään yleensä yhdistelmälogiikkapiirien toteuttamiseen. PLA: lla on joukko ohjelmoitavia JA-tasoja (AND-matriisi), jotka linkittyvät ohjelmoitavien TAI-tasojen joukkoon (TAI-taulukko), joita voidaan sitten täydentää väliaikaisesti tuotoksen tuottamiseksi. Tämän asettelun avulla voidaan syntetisoida suuri määrä logiikkatoimintoja tuotteiden summa (SOP) kanoniset muodot. Yksinkertainen PLA-lohkokaavio on annettu alla.

PLA: n lohkokaavio

Tärkein ero PLA: n ja PAL: n (ohjelmoitava matriisilogiikka) välillä on

PLA: Molemmat JA taso tai TAI taso ovat ohjelmoitavia.

PAL: Vain JA-taso on ohjelmoitavissa, kun taas TAI-taso on kiinteä.

PLA: n paremman ymmärtämisen vuoksi harkitsemme alla olevaa esimerkkiä.

Yritetään toteuttaa nämä funktiot f1 ja f2 annetaan muodossa

Tulot x1, x2, x3 ja niiden vastaavat komplementoidut signaalit annetaan ohjelmoitavalle JA-tasolle, siellä saamme JA-tasolähdöt P1-, P2-, P3-kutsutuiksi mintermeiksi. Sitten nämä signaalit annetaan ohjelmoitavalle TAI-tasolle vaaditun lähtöfunktion f1 ja f2 tuottamiseksi (tuotteiden summa). Seuraava kuva kuvaa PLA: n porttitason toteutuksen tietylle toiminnallisuudelle.

PLA: n täytäntöönpano

Kyse on peräkkäisten piirien suunnittelusta PLA: n avulla. Katsomme, että tässä artikkelissa annetut tiedot auttavat sinua ymmärtämään paremmin tätä käsitettä. Lisäksi kaikki tähän artikkeliin liittyvät kysymykset tai ohjeet sähkö- ja elektroniikkaprojektien toteuttaminen , voit ottaa meihin yhteyttä kommentoimalla alla olevassa kommenttiosassa. Tässä on kysymys sinulle, Mitä tarkoitetaan peräkkäisellä piirillä?