Elektroniikan alalla tärkein käsite, jolla jokainen komponentti toimii, on Logiikkaportit ”. Logiikkaporttien käsite on toteutettu kaikissa toiminnoissa, kuten integroiduissa piireissä, antureissa, kytkentätarkoituksissa, mikro-ohjaimissa ja prosessoreissa, salauksen ja salauksen purkamisen tarkoituksissa ja muissa. Näiden lisäksi Logic Gatesilla on laaja sovellus. Loogisia portteja on monenlaisia, kuten summain, vähennyslaskuri, täysi Lisääjä , Täysi vähittäiskauppias, Puolisubtraktori ja monet muut. Joten tässä artikkelissa on kollektiivisia tietoja puoli vähennyspiiri , puolet vähennyslaskijan totuustaulukosta ja siihen liittyvät käsitteet.

Mikä on puolisubtraktori?

Ennen kuin menemme keskustelemaan puolisubtraktorista, meidän on tiedettävä binäärinen vähennyslasku. Binaarisessa vähennyslaskussa vähennysprosessi on samanlainen kuin aritmeettinen vähennys. Aritmeettisessa vähennyksessä käytetään perusnumerojärjestelmää, kun taas binäärisessä vähennyslaskussa binäärilukuja käytetään vähennykseen. Tuloksena olevat ehdot voidaan merkitä erolla ja lainata.

Puoli vähennyslaskija on tärkein yhdistelmälogiikkapiiri jota käytetään digitaalinen elektroniikka . Pohjimmiltaan tämä on elektroninen laite tai toisin sanoen voimme sanoa sen logiikkapiirinä. Tätä piiriä käytetään kahden binääriluvun vähennyksen suorittamiseen. Edellisessä artikkelissa olemme jo keskustelleet puolisumman ja täyden summaimen piirien käsitteet joka käyttää laskelmissa binäärilukuja. Samoin vähennyspiiri käyttää binäärilukuja (0,1) vähennykseen. Puolisubtraktorin piiri voidaan rakentaa kahdella logiikkaportit, nimittäin NAND- ja EX-OR-portit . Tämä piiri antaa kaksi elementtiä, kuten eron, samoin kuin ne lainaa.

Kuten binäärisissä vähennyslaskelmissa, pääluku on 1, voimme tuottaa lainaa, kun taas subtrahend 1 on parempi kuin minuend 0, ja tästä johtuen lainaa tarvitaan. Seuraava esimerkki antaa kahden binääribitin binäärisen vähennyksen.

Ensimmäinen numero | Toinen numero | Ero | Lainata |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Edellä olevassa vähennyslaskussa kaksi numeroa voidaan esittää A: lla ja B: llä. Nämä kaksi numeroa voidaan vähentää ja antaa tulokseksi saadut bitit erona ja lainata.

Kun tarkkailemme kahta ensimmäistä ja neljää riviä, näiden rivien välinen ero, niin ero ja laina ovat samanlaiset, koska osa-ala on pienempi kuin minuend. Samoin, kun havaitaan kolmas rivi, minuendiarvo vähennetään alitunnistuksesta. Joten ero ja lainabitit ovat 1, koska alitunnusnumero on parempi kuin minuendin numero.

Tämä yhdistelmäpiiri on välttämätön työkalu kaikenlaisille digitaalinen piiri tietää tulojen ja lähtöjen mahdolliset yhdistelmät. Esimerkiksi, jos vähennyslaskijalla on kaksi tuloa, tuloksena olevat lähdöt ovat neljä. Puoli vähennyslaskijan o / p mainitaan alla olevassa taulukossa, mikä merkitsee erobittiä ja lainabittiä. Piirin totuustaulukon selitys voidaan tehdä käyttämällä logiikkaportteja, kuten EX-OR-logiikkaportti ja AND-portti, jota seuraa EI-portti.

Totuustaulukon ratkaiseminen K-kartta näkyy alla.

puoliksi vähennyslasku k kartta

puoli vähennyslaskijan lauseketta totuustaulukon ja K-kartan avulla voidaan johtaa

Ero (D) = ( x’y + xy ')

= x ⊕ y

Laina (B) = x’y

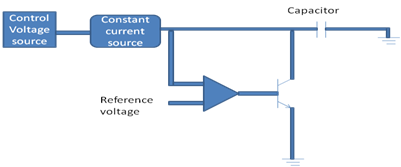

Looginen piiri

puoliksi vähennyslaskijan looginen piiri voidaan selittää käyttämällä logiikkaportteja:

- 1 XOR-portti

- 1 EI porttia

- 1 JA portti

Edustus on

Puoli vähennyslaskijan looginen piiri

Puolisubtraktorin lohkokaavio

Puolisubtraktorin lohkokaavio on esitetty yllä. Se vaatii kahta tuloa ja antaa kaksi lähtöä. Tässä tulot on esitetty A & B: llä, ja lähdöt ovat Ero ja Laina.

Yllä oleva piiri voidaan suunnitella EX-OR & NAND -portilla. Tässä NAND-portti voidaan rakentaa käyttämällä portteja JA EI. Joten tarvitsemme kolme logiikkaporttia puoli vähennyspiirin muodostamista varten, nimittäin EX-OR-portti, EI portti ja NAND-portti.

AND- ja NOT-porttien yhdistelmä tuottaa erilaisen yhdistetyn portin nimeltä NAND Gate. Ex-OR-portin lähtö on Difference-bitti ja NAND Gate -lähtö on Borrow-bitti samoille tuloille A&B.

AND-Gate

AND-gate on yhden tyyppinen digitaalinen logiikkaportti, jossa on useita sisääntuloja ja yksi lähtö ja joka suorittaa tuloyhdistelmien perusteella loogisen yhteyden. Kun tämän portin kaikki tulot ovat korkeat, lähtö on suuri, muuten lähtö on matala. AND-portin ja totuustaulukon logiikkakaavio on esitetty alla.

JA portti- ja totuuspöytä

EI porttia

NOT-gate on yhden tyyppinen digitaalinen logiikkaportti, jolla on yksi sisääntulo, ja lähtötulon perusteella lähtö muutetaan. Esimerkiksi, kun NOT-portin tulo on korkea, lähtö on matala. NOT-gate-logiikkakaavio totuustaulukon kanssa on esitetty alla. Käyttämällä tämän tyyppistä logiikkaporttia voimme suorittaa NAND- ja NOR-portit.

EI portin ja totuuden taulukko

Ex-OR-portti

Exclusive-OR- tai EX-OR-portti on yhden tyyppinen digitaalinen logiikkaportti, jossa on 2 tuloa ja yksi lähtö. Tämän logiikkaportin toiminta riippuu TAI-portista. Jos joku tämän portin tuloista on korkea, EX-OR-portin lähtö on korkea. EX-OR: n symboli- ja totuustaulukko on esitetty alla.

XOR-portin ja totuuden taulukko

Half Subtractor -piiri Nand Gatea käyttäen

Vähentäjän suunnittelu voidaan tehdä käyttämällä logiikkaportteja kuten NAND-portti ja Ex-OR-portti. Tämän puolisubtraktoripiirin suunnittelemiseksi meidän on tiedettävä kaksi käsitettä, nimittäin ero ja laina.

Half Subtractor -piiri Nand Gatea käyttäen

Jos seuraamme varovasti, on melko selvää, että tämän piirin suorittama operaation moninaisuus, joka liittyy tarkasti EX-OR-portin toimintaan. Siksi voimme yksinkertaisesti käyttää EX-OR-porttia muutokseen. Samalla tavoin puolisummutuspiirin tuottama laina voidaan saavuttaa yksinkertaisesti käyttämällä loogisten porttien sekoitusta, kuten AND- gate ja NOT-gate.

Tämä HS voidaan suunnitella myös käyttämällä NOR-portteja, jos se vaatii 5 NOR-porttia rakentamiseen. NOR-portteja käyttävä piirikaavio puoli vähennyslaskija on esitetty seuraavasti:

Puolisubtraktori, joka käyttää Nor Gatesia

Totuus taulukko

Ensimmäinen bitti | Toinen bitti | Ero (EX-OR Out) | Lainata (NAND Out) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

VHDL- ja Testbench-koodi

Puolisubtraktorin VHDL-koodi selitetään seuraavasti:

kirjasto IEEE

käytä IEEE.STD_LOGIC_1164.ALL

käytä IEEE.STD_LOGIC_ARITH.ALL

käytä IEEE.STD_LOGIC_UNSIGNED.ALL

kokonaisuus Half_Sub1 on

Portti (a: STD_LOGIC

b: STD_LOGICissa

HS_Diff: ulos STD_LOGIC

HS_Borrow: ulos STD_LOGIC)

loppu Half_Sub1

arkkitehtuuri Half_Sub1: n käyttäytyminen on

alkaa

HS_ero<=a xor b

HS_Laina<=(not a) and b

testipenkkikoodi HS: lle selitetään seuraavasti:

KIRJASTO IEEE

KÄYTÄ ieee.std_logic_1164.ALL

ENTITY HS_tb IS

LOPPU HS_tb

ARKITEHTUURI HS_tb / HS_tb IS

KOMPONENTTI HS

PORTTI (a: IN std_logic

b: IN std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

LOPETA KOMPONENTTI

signaali a: std_logic: = ’0’

signaali b: std_logic: = ’0’

signaali HS_Diff: std_logic

signaali HS_Borrow: std_logic

ALKAA

uut: HS PORT MAP (

a => a,

b => b,

HS_erotus => HS_erotus,

HS_lainaa => HS_lainaa

)

stim_proc: prosessi

alkaa

että<= ‘0’

b<= ‘0’

odota 30 ns

että<= ‘0’

b<= ‘1’

odota 30 ns

että<= ‘1’

b<= ‘0’

odota 30 ns

että<= ‘1’

b<= ‘1’

odota

lopeta prosessi

LOPPU

Täysi vähennyslaskuri käyttämällä puolisubtraktoria

Täysi vähennyslasku on yhdistelmälaite, joka käyttää vähennysfunktiota käyttämällä kahta bittiä ja on minuend ja subtrahend. Piiri ottaa lainaksi edellisen lähdön ja sillä on kolme tuloa kahdella lähdöllä. Kolme tuloa ovat minuend, subtrahend ja tulo, joka on saatu edellisestä lainasta, ja kaksi lähtöä ovat ero ja laina.

Täysi vähennyslaskun looginen kaavio

Totuus taulukko täysi vähennyslaskuri On

| Tulot | Lähdöt | |||

| X | Y | Yin | FS_ero | FS_Laina |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Yllä olevan totuustaulukon avulla loogisen kaavion mainospiirikaavio täydellisen vähennyslaskijan toteuttamiseksi käyttämällä puoli vähennyslaskijoita on esitetty alla:

Täysi vähittäiskauppias käyttäen HS: tä

Puolisubtraktorin edut ja rajoitukset

Puolisubtraktorin edut ovat:

- Tämän piirin toteuttaminen ja rakentaminen on yksinkertaista ja helppoa

- Tämä piiri kuluttaa vähän virtaa digitaalisessa signaalinkäsittelyssä

- laskennalliset toiminnot voidaan suorittaa paremmilla nopeuksilla

Tämän yhdistelmäpiirin rajoitukset ovat:

Vaikka puoli vähennyslaskijaa käytetään laajasti monissa toiminnoissa ja toiminnoissa, rajoituksia on vähän ja ne ovat:

- Puoli vähennyspiiriä ei hyväksy 'lainaa' edellisistä lähdöistä, jos tämä on tämän piirin ratkaiseva haittapuoli

- Koska monet reaaliaikaiset sovellukset toimivat lukuisien bittien lukumäärän vähentämisellä, puoliksi vähennyslaitteilla ei ole kykyä vähentää monta bittiä

Half Subtractor -sovellukset

Puolisubtraktorin sovellukset sisältävät seuraavat.

- Puolisubtraktoria käytetään ääni- tai radiosignaalien voiman vähentämiseen

- Se voi olla käytetään vahvistimissa vähentää äänen vääristymistä

- Puolet vähennyslaskurista on käytetään prosessorin ALU: ssa

- Sitä voidaan käyttää operaattoreiden kasvattamiseen ja vähentämiseen, ja se laskee myös osoitteet

- Puolisubtraktoria käytetään vähiten merkitsevien sarakkeiden numeroiden vähentämiseen. Moninumeroisten lukujen vähentämiseen sitä voidaan käyttää LSB: lle.

Siksi yllä olevasta puolisubtraktoriteoriosta voimme viimeinkin sulkea, että käyttämällä tätä piiriä voimme vähentää yhdestä binääribitistä toisesta tuotosten, kuten Ero ja Laina, tuottamiseksi. Vastaavasti voimme suunnitella puolisubtraktorin käyttämällä NAND-porttipiiriä sekä NOR-portteja. Muut tunnettavat käsitteet ovat puoliksi vähennyslaskijan verilog-koodi ja kuinka RTL-kaaviokuva voidaan piirtää?