Yleensä täysi vähennyslaskija on yksi käytetyimmistä ja välttämättömät yhdistelmälogiikkapiirit . Se on peruselektroniikkalaite, jota käytetään kahden binääriluvun vähentämiseen. Aikaisemmassa artikkelissa olemme jo antaneet perusteorian puoli summain ja täysi summa joka käyttää binäärilukuja laskennassa. Samoin täyssubtraktori käyttää binäärilukuja, kuten 0,1, vähennykseen. Tämän piiri voidaan rakentaa logiikkaporteilla, kuten OR, Ex-OR, NAND gate. Tämän vähennyslaskurin tulot ovat A, B, Bin ja lähdöt ovat D, Bout.

Tämä artikkeli antaa täyden vähennyslaskijan teoriaidean, joka sisältää tilat, kuten mikä on vähennyslaskija, suunnittelu logiikkaporteilla, totuustaulukko jne. Tämä artikkeli on hyödyllinen insinööriopiskelijoille, jotka voivat käydä läpi nämä aiheet HDL-käytännön laboratoriossa.

Mikä on vähennyslasku?

Binäärilukujen vähennys voidaan tehdä vähennyspiirin avulla. Tämä on eräänlainen yhdistelmälogiikkapiiri, jota käytetään kahden binääriluvun, kuten 0 ja 1, vähentämiseen. Binaaristen numeroiden vähentäminen 0: sta 0: een tai 0: sta 1: een ei muuta tulosta, 1: n 1: n vähentäminen johtaa 0: een, mutta 1: n 0: n vähennys tarvitsee lainata.

Esimerkiksi kaksibittinen vähennyspiiri sisältää kaksi tuloa, kuten A ja B, kun taas lähdöt ovat eroja ja lainaa. Tämä piiri voidaan rakentaa summaimilla yhdessä taajuusmuuttajien kanssa, jotka sijaitsevat jokaisen datasyötön sekä lainatun (bin) -tulon välillä FA: n aikaisemmassa vaiheessa.

Vähennyslaskijat luokitellaan kahteen tyyppiin, kuten puoli- ja täysi vähennyslaskija. Tässä keskustelemme koko vähennyslaskijasta.

Mikä on täysi vähennyslasku?

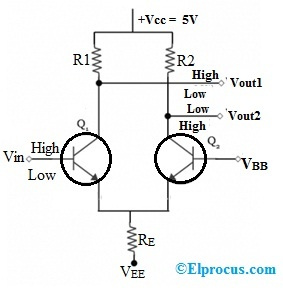

Se on elektroninen laite tai logiikkapiiri joka suorittaa kahden binääriluvun vähennyksen. Se on yhdistelmälogiikkapiiri, jota käytetään digitaalisessa elektroniikassa. Monet yhdistelmäpiirit ovat saatavilla integroidun piirin tekniikka nimittäin summaimet, kooderit, dekooderit ja multiplekserit. Tässä artikkelissa aiomme keskustella sen rakentamisesta käyttämällä puolisubtraktoria ja myös termejä, kuten totuustaulukko.

Täysi vähittäiskauppias

Tämän voi suunnitella kaksi puoli vähennyslaskijaa, johon sisältyy kolme syötettä, kuten minuend, subtrahend ja lainata, lainata bitti tulojen joukosta saadaan vähentämällä kaksi binäärilukua ja vähennetään seuraavasta ylemmän asteen parista bittiä, tuotoksia erona ja lainaa.

täydellinen vähennyslaskijan lohkokaavio näkyy alla. Puolisubtraktorin tärkein haittapuoli on, emme voi tehdä lainan bittiä tässä vähennyslaskussa. Vaikka sen suunnittelussa voimme itse asiassa tehdä lainasta bitin piirissä ja voimme vähentää jäljellä olevilla kahdella i / ps: llä. Tässä A on minuend, B on subtrahend ja Bin lainaa sisään. Lähdöt ovat Difference (Diff) ja Bout (Borrow out). Täydellinen vähennyspiiri voidaan saada käyttämällä kahta puolisubtraktoria ylimääräisellä TAI-portilla.

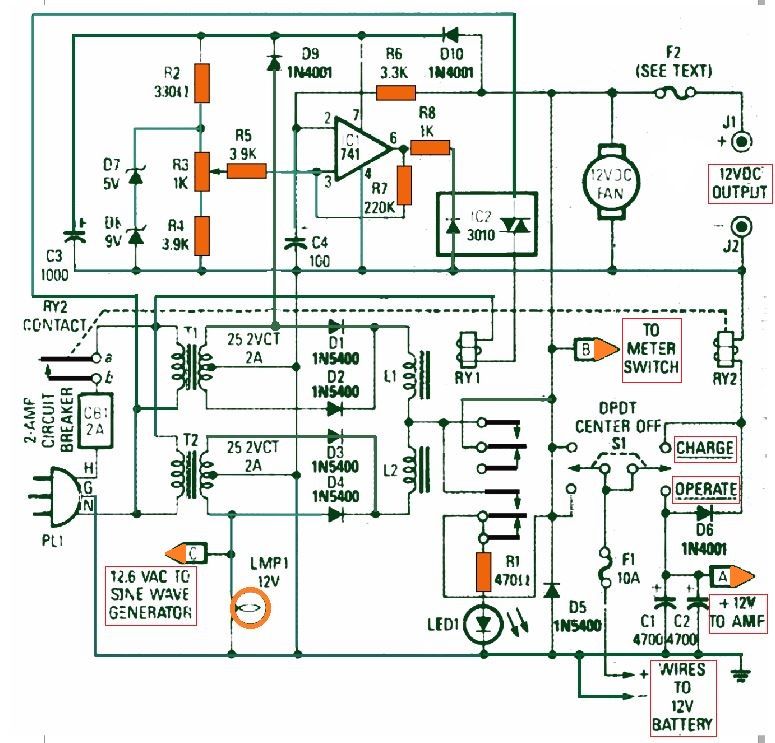

Täysi vähennyslaskijan piirikaavio logiikkaporteilla

piirikaavio täydestä vähennyslaskijasta käyttäen perusporttia s on esitetty seuraavassa lohkokaaviossa. Tämä piiri voidaan tehdä kahdella puolisubtraktoripiirillä.

Alkuperäisessä puolisubtraktoripiirissä binääritulot ovat A ja B. Kuten olemme keskustelleet edellisessä puolisubtraktoriartikkelissa, se tuottaa kaksi lähtöä, nimittäin ero (Diff) & Borrow.

Täysi alihankkija logiikkaportteja käyttämällä

Vasemman vähennyslaskurin ero o / p annetaan vasemman puoli-vähennyslaskijan piirille. Diffuusiolähtö toimitetaan edelleen oikean puolikkaan vähennyspiirin tuloon. Tarjoimme lainaa bitissä seuraavien muiden i / p: n kautta puoli vähennyspiiri . Jälleen kerran se antaa Diffille sekä lainaa vähän. Tämän vähennyslaskun lopullinen tulos on Diff-lähtö.

Toisaalta laina molemmista puolisubtraktoripiireistä on kytketty TAI-logiikkaporttiin. Myöhemmin kuin annamme TAI-logiikkaa vähennyslaskijan kahdelle lähtöbitille, hankimme lopullisen lainan vähennyslaskijalta. Viimeinen lainaus merkitsee MSB: tä (merkittävin bitti).

Jos havaitsemme tämän sisäisen piirin, voimme nähdä kaksi Half Subtractoria NAND-portilla ja XOR-portilla ylimääräisellä TAI-portilla.

Täysi vähennyslaskijan totuustaulukko

Tämä vähennyslaskuripiiri suorittaa vähennyslaskun kahden bitin välillä, jolla on 3 tuloa (A, B ja Bin) ja kaksi lähtöä (D ja Bout). Tässä syötteet osoittavat minuendia, subtrahendia ja edellistä lainaa, kun taas kaksi lähtöä merkitään lainaksi o / p ja erona. Seuraava kuva näyttää täyden vähennyslaskijan totuustaulukon.

Tulot | Lähdöt | |||

Minuend (A) | Subtrahend (B) | Laina (alusta) | Ero (D) | Laina (ottelu) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

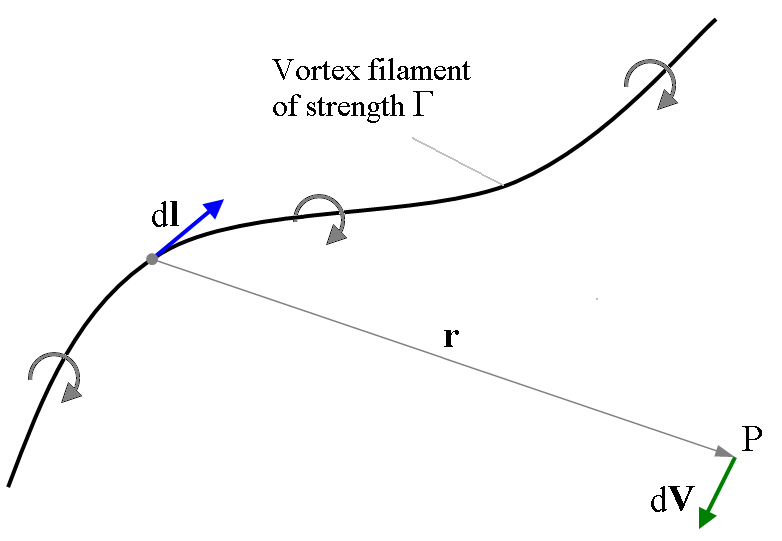

K-kartta

Ohjelman yksinkertaistaminen täydellinen vähennyslaskija K-kartta yllä oleva ero ja laina on esitetty alla.

Eroyhtälöt sekä Bin mainitaan alla.

Ilmaisu ero on,

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

Laina lainaa on,

Ottelu = A'Bin + A'B + BBin

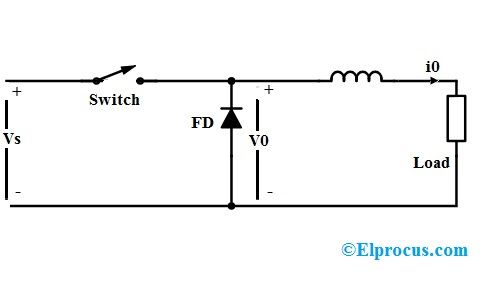

Täyden vähennyspiirin kaskadi

Aikaisemmin olemme keskustelleet yleiskatsauksesta tästä, kuten rakentamisesta, kytkentäkaaviosta logiikkaporteilla. Mutta jos haluamme vähentää kaksi muuten enemmän 1-bittistä lukua, tämä vähennyspiiri on erittäin hyödyllinen yksittäisten bittilukujen kaskadissa ja vähentää myös enemmän kuin kaksi binaarilukua. Tällaisissa tapauksissa käytetään täyden summaimen kaskadoitua virtapiiriä EI logiikkaportin avulla. Piirin muuntaminen täydestä summaimesta täydelliseksi vähennyslaskijaksi voidaan suorittaa käyttämällä 2: n komplementtitekniikkaa.

Yleensä käännä koko summaimen subtrahend-tulot käyttämällä EI porttia, muuten invertteriä. Lisäämällä tämä Minuend (ei-käänteinen tulo) & Subtrahend (käänteinen tulo), FA-piirin LSB (kantotulo) on 1, mikä tarkoittaa Logic High -arvoa, muuten vähennämme kaksi binaarista numeroa 2: n komplementtitekniikalla. FA: n lähtö on Diff-bitti ja jos käännämme suorituksen käänteiseksi, voimme saada MSB: n muuten Borrow-bitin. Itse asiassa voimme suunnitella piirin siten, että lähtö voidaan havaita.

Verilog-koodi

Koodaavan osan osalta meidän on ensin tarkistettava logiikkapiirikaavion rakenteellinen malli. Tämän logiikkakaavio voidaan rakentaa käyttämällä AND-porttia, puoli vähennyspiiriä ja loogisten porttien yhdistelmää, kuten AND, OR, NOT, XOR-portit. Kuten rakennemallinnuksessa, selitämme erilaisia moduuleja jokaiselle peruselementtijärjestelmälle. Seuraavassa koodissa eri moduulit voidaan määrittää jokaiselle portille.

Tämä moduuli on tarkoitettu OR-portille.

TULO: a0, b0

LÄHTÖ: c0

Lopuksi yhdistämme nämä porttitarkat moduulit ainoaksi moduuliksi. Tätä varten tässä käytetään moduulin instantointia. Nyt tätä esimerkkiä voidaan käyttää, kun haluamme kopioida tarkka moduuli tai toiminto erilaisille tulojoukoille. Ensin suunnitellaan puoli vähennyslaskijaa ja sitten tätä moduulia käytetään täyden vähennyslaskun toteuttamiseen. Tämän toteuttamiseksi käytämme OR-porttia yhdistämään o / ps Bout-muuttujalle. verilog-koodi koko vähennyslaskijalle näkyy alla

moduuli or_gate (a0, b0, c0)

tulo a0, b0

lähtö c0

määritä c0 = a0 | b0

endmoduuli

moduuli xor_gate (a1, b1, c1)

tulo a1, b1

lähtö c1

määritä c1 = a1 ^ b1

endmoduuli

moduuli and_gate (a2, b2, c2)

tulo a2, b2

lähtö c2

määritä c2 = a2 & b2

endmoduuli

moduuli not_gate (a3, b3)

tulo a3

lähtö b3

määritä b3 = ~ a3

endmoduuli

moduuli half_subtractor (a4, b4, c4, d4)

tulo a4, b4

lähtö c4, d4

johto x

xor_gate u1 (a4, b4, c4)

and_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

endmoduuli

moduuli full_subtractor (A, B, Bin, D, Bout)

tulo A, B, Bin

lähtö D, Bout

lanka p, q, r

puoli-alihankkija u4 (A, B, p, q)

puoli-alihankkija u5 (p, Bin, D, r)

or_gate u6 (q, r, ottelu)

endmoduuli

Täysi vähennyslasin käyttäen 4X1-multiplekseria

Vähennyslasku voidaan suorittaa kahden komplementtimenetelmän avulla. Siksi vaaditaan 1-XOR-portin käyttöä, jota käytetään kääntämään 1-bittinen ja sisällyttämään yksi siirtobitiin. DIFFERENCE-lähtö on samanlainen kuin koko summainpiirin lähtö SUM, mutta BARROW o / p ei ole samanlainen kuin täydellisen summaimen kantolähtö, mutta se on käännetty ja täydennetty, kuten A - B = A + (-B) = A + kahden komplementti B.

Tämän suunnittelu 4X1-multiplekserin avulla on esitetty seuraavassa logiikkakaaviossa. Tämä suunnittelu voidaan tehdä seuraavilla vaiheilla.

4X1-multiplekseri

- Vaiheessa 1 on kaksi lähtöä, kuten Sub ja Borrow. Joten meidän on valittava 2 multiplekseria.

- Vaiheessa 2 totuustaulukko voidaan toteuttaa yhdessä K-karttojen kanssa

- Vaiheessa 3 kaksi muuttujaa voidaan valita valitsemallesi riville. Esimerkiksi B & C ovat tässä tapauksessa.

Totuus taulukko

totuuden vähennyslaskijan totuustaulukko 4X1-multiplekseria käyttävä piiri sisältää seuraavat

TO | B | C | Sub | Lainata |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

Täysi vähennyslaskuri dekooderilla

Täyden vähennyslaskurin suunnittelu 3-8 dekooderilla voidaan tehdä käyttämällä aktiivisia matalia lähtöjä. Oletetaan, että dekooderi toimii seuraavan logiikkakaavion avulla. Dekooderissa on kolme tuloa 3-8 dekooderissa. Totuustaulukon perusteella voimme kirjoittaa mintermit erojen ja lainojen tuotoksille.

Yllä olevasta totuustaulukosta

Totuustaulukon eri toimintoja varten mintermermit voidaan kirjoittaa 1,2,4,7: ksi, ja vastaavasti lainaa varten mintermermit voidaan kirjoittaa 1,2,3,7: ksi. 3-8 dekooderissa on kolme tuloa sekä 8 lähtöä, kuten 0-7 numeroa.

3-8-dekooderi

Jos vähennyslaskun tulo on 000, lähtö '0' on aktiivinen ja jos tulo on 001, lähtö '1' on aktiivinen.

Nyt vähennyslaskimen lähdöt voidaan ottaa 1, 2, 4 ja 7 liittääksesi se NAND-porttiin, silloin lähtö on ero. Nämä lähdöt voidaan liittää muihin NAND-logiikkaportteihin, joissa lähtö muuttuu lainaksi.

Esimerkiksi, jos tulo on 001, niin lähtö on 1, mikä tarkoittaa, että se on aktiivinen. Joten lähtö on aktiivinen matala ja lähtö voidaan saada NAND-portista, jota kutsutaan erotusfunktioksi, kuten korkea, ja lainatoiminto muuttuu myös korkeaksi. Siksi saamme ensisijaisen tuotoksen. Joten lopuksi dekooderi toimii kuin täysi vähennyslaite.

Hyödyt ja haitat

vähennyslaskun edut Sisällytä seuraavat.

- Vähentäjän suunnittelu on hyvin yksinkertaista sekä toteutus

- Tehon vähennys DSP: ssä (digitaalinen signaalinkäsittely)

- Laskennalliset tehtävät voidaan suorittaa suurella nopeudella.

vähennyslaskun haittoja Sisällytä seuraavat.

- Puolisubtraktorissa ei ole ehtoa hyväksyä Borrow-tyyppistä syötettä aikaisemmasta vaiheesta.

- Vähennysnopeus voi olla osittainen piirin viiveen kautta.

Sovellukset

Jotkut täyssubtraktorin sovellukset Sisällytä seuraavat

- Näitä käytetään yleensä tietokoneiden ALU: ssa (aritmeettinen logiikkayksikkö) vähentämään prosessoreina ja grafiikkasuoritina grafiikan sovelluksille piirin vaikeuksien vähentämiseksi.

- Vähennyslaskijoita käytetään useimmiten aritmeettisten toimintojen, kuten vähennyslaskun, suorittamiseen elektronisissa laskimissa ja digitaalisissa laitteissa.

- Näitä sovelletaan myös erilaisia mikro-ohjaimia aritmeettiseen vähennykseen, ajastimiin ja ohjelmalaskuriin (PC)

- Vähentäjiä käytetään prosessoreissa laskemaan taulukoita, osoitteita jne.

- Se on hyödyllinen myös DSP- ja verkkopohjaisiin järjestelmiin.

- Näitä käytetään pääasiassa tietokoneiden ALU: han, kuten grafiikkasovellusten, kuten CPU ja GPU, vähentämiseen piirin monimutkaisuuden vähentämiseksi.

- Näitä käytetään pääasiassa aritmeettisten toimintojen suorittamiseen, kuten vähennyslasku digitaalisissa laitteissa, laskimissa jne.

- Nämä vähennyslaskurit soveltuvat myös erilaisille mikro-ohjaimille ajastimille, PC: lle (ohjelmalaskuri) ja aritmeettiselle vähennykselle

- Näitä käytetään prosessoreille osoitteiden, taulukoiden jne. Laskemiseen.

- Tämän toteuttaminen loogisilla portteilla, kuten NAND & NOR, voidaan tehdä millä tahansa täydellä vähennyslaskijan logiikkapiirillä, koska molempia NOR & NAND -portteja kutsutaan universaaleiksi porteiksi.

Yllä olevista tiedoista arvioimalla summain, täydellinen vähennyslaskuri käyttämällä kahta puoli vähennyslaskijapiiriä ja sen taulukkomuodot, voidaan huomata, että täyden vähennyslaskun Dout on tarkalleen samanlainen kuin täyden summaimen Sout. Ainoa muunnelma on, että A (syöttömuuttuja) täydennetään täyden vähennyslaskussa. Siten on mahdollista vaihtaa täysi summainpiiri täyssubtraktoriksi täydentämällä vain i / p A: ta ennen kuin se annetaan logiikkaportit viimeisen lainabittilähdön (Bout) luomiseksi.

Käyttämällä mitä tahansa täydellistä vähennyslaskijan logiikkapiiriä, NAND-portteja käyttävä täysi vähennyslaskija ja täyttä vähennyslaskijaa käyttäviä eikä portteja voidaan toteuttaa, koska sekä NAND- että NOR-portteja kohdellaan universaaleina portteina. Tässä on kysymys sinulle, mikä on ero puolisubtraktorin ja täyden vähennyslaskun välillä?