Käskyjoukko tai käskyjoukkoarkkitehtuuri on tietokoneen rakenne, joka antaa tietokoneelle komentoja ohjaamaan tietojenkäsittelyä. Ohjesarja koostuu ohjeista, osoitetiloista, alkuperäisistä tietotyypeistä, rekistereistä, keskeytyksistä, poikkeusten käsittelystä ja muistiarkkitehtuurista. Ohjesarja voidaan jäljitellä ohjelmistossa tulkin avulla tai sisäänrakennettuna prosessorin laitteistoon. Ohjesarjaarkkitehtuuria voidaan pitää rajana ohjelmiston ja laitteiston välillä. Mikrokontrollerien luokitus ja mikroprosessorit voidaan tehdä RISC- ja CISC-käskyjoukkoarkkitehtuurin perusteella.

Suoritin

Ohjesarja määrittää prosessorin toiminnot, mukaan lukien prosessorin tukemat toiminnot, prosessorin tallennusmekanismit ja tavan ohjelmoida ohjelmat prosessorille.

Mikä on RISC ja CISC?

RISC ja CISC voidaan laajentaa seuraavasti:

RISC edustaa supistettua käskysarjatietokonetta ja

CISC edustaa Complex Instruction Set Computer -tietokonetta.

RISC (Reduced Instruction Set Computer) -arkkitehtuuri

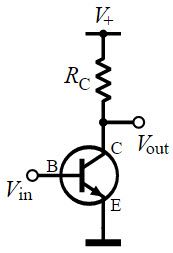

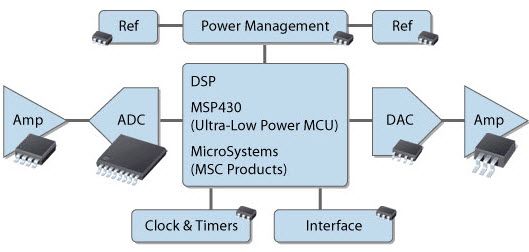

RISC-arkkitehtuuri

mikro-ohjaimen arkkitehtuuri Pieniä ja erittäin optimoituja käskyjä hyödyntävää komentoa kutsutaan pienennetyksi ohjeistustietokoneeksi tai yksinkertaisesti kutsutaan RISC: ksi. Sitä kutsutaan myös nimellä LOAD / STORE -arkkitehtuuri.

1970-luvun lopulla ja 1980-luvun alussa RISC-hankkeita kehitettiin pääasiassa Stanfordin, UC-Berkleyn ja IBM: n toimesta. John Coke IBM: n tutkimusryhmästä kehitti RISC: n vähentämällä laskelmien käsittelyyn tarvittavien ohjeiden määrää nopeammin kuin CISC. RISC-arkkitehtuuri on nopeampi ja RISC-arkkitehtuurin valmistukseen tarvittavat sirut ovat myös halvempia kuin CISC-arkkitehtuuri.

RISC-arkkitehtuurin tyypillisiä piirteitä

- RISC: n putkilinjaustekniikka suorittaa useita käskyjen osia tai vaiheita samanaikaisesti siten, että jokainen CPU: n käsky on optimoitu. Siksi RISC-prosessoreilla on kello per käsky yhden jakson ajan, ja tätä kutsutaan yhden jakson suoritukseksi.

- Se optimoi rekisterin käyttö RISC: ssä on enemmän rekistereitä ja enemmän muistissa olevia vuorovaikutuksia voidaan estää.

- Yksinkertaiset osoitetilat, jopa monimutkaiset osoitteet voidaan tehdä aritmeettisesti JA / TAI loogiset operaatiot .

- Se yksinkertaistaa kääntäjän suunnittelua käyttämällä identtisiä yleiskäyttöisiä rekistereitä, joiden avulla mitä tahansa rekisteriä voidaan käyttää missä tahansa yhteydessä.

- Rekisterien tehokasta käyttöä ja putkilinjan käytön optimointia varten tarvitaan pienempi käskyjoukko.

- Opkoodissa käytettyjen bittien lukumäärä pienenee.

- RISC: ssä on yleensä vähintään 32 rekisteriä.

RISC-prosessorin arkkitehtuurin edut

- RISC: n pienten ohjeiden takia korkean tason kielen kääntäjät voivat tuottaa tehokkaamman koodin.

- RISC sallii vapaan tilan käytön mikroprosessorit sen yksinkertaisuuden vuoksi.

- Stackin käyttämisen sijaan monet RISC-prosessorit käyttävät rekistereitä argumenttien välittämiseen ja paikallisten muuttujien pitämiseen.

- RISC-toiminnot käyttävät vain muutamia parametreja, eivätkä RISC-prosessorit voi käyttää puheluohjeita ja siksi käyttää kiinteän pituisia ohjeita, jotka on helppo toimittaa.

- Operaation nopeus voidaan maksimoida ja suoritusaika voidaan minimoida.

- Tarvitaan hyvin pieni määrä käskyformaatteja (alle neljä), muutama määrä käskyjä (noin 150) ja muutama osoitetila (alle neljä).

RISC-prosessorin arkkitehtuurin haitat

- Ohjeiden pituuden lisääntyessä RISC-prosessoreiden monimutkaisuus kasvaa suoritettavien komentosarjojensa vuoksi.

- RISC-prosessorien suorituskyky riippuu enimmäkseen kääntäjästä tai ohjelmoijasta, koska kääntäjän tietämyksellä on tärkeä rooli samalla, kun CISC-koodi muunnetaan RISC-koodiksi, joten luodun koodin laatu riippuu kääntäjästä.

- Vaikka CISC-koodi ajoitetaan RISC-koodiksi, jota kutsutaan koodilaajennukseksi, koko kasvaa. Ja tämän koodilaajennuksen laatu riippuu jälleen kääntäjästä ja myös koneen käskyjoukosta.

- RISC-prosessorien ensimmäisen tason välimuisti on myös RISC: n haitta, jossa näillä prosessoreilla on suuret muistivälimuistit itse sirussa. Ohjeiden syöttämiseen ne vaativat hyvin nopeat muistijärjestelmät .

CISC (Complex Instruction Set Computer) -arkkitehtuuri

CISC-prosessoriarkkitehtuurin päätarkoitus on suorittaa tehtävä käyttämällä vähemmän kokoonpanolinjoja. Tätä tarkoitusta varten prosessori on rakennettu suorittamaan useita toimintoja. Monimutkaisia ohjeita kutsutaan myös nimellä MULT, joka toimii muistipankit suoraan tietokoneesta kääntämättä kääntäjää suorittamaan tallennus- ja lataustoimintoja.

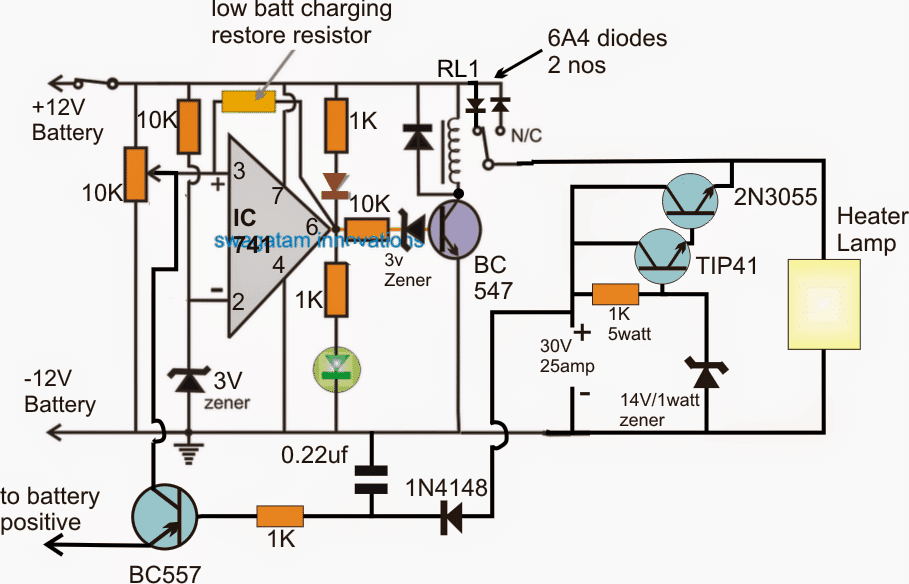

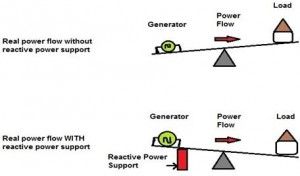

CISC-arkkitehtuuri

CISC-arkkitehtuurin ominaisuudet

- Tietokonearkkitehtuurin yksinkertaistamiseksi CISC tukee mikroprogrammointia.

- CISC: llä on enemmän ennalta määritettyjä ohjeita, mikä tekee korkean tason kielistä helppoa suunnitella ja toteuttaa.

- CISC koostuu vähemmän rekistereistä ja useammasta osoitetilasta, yleensä 5-20.

- CISC-prosessori vie vaihtelevaa jaksoaikaa komentojen suorittamiseen - monikellojaksoja.

- CISC: n monimutkaisen käskyjoukon takia putkistotekniikka on erittäin vaikeaa.

- CISC koostuu useammasta käskystä, yleensä 100: sta 250: een.

- Erityisiä ohjeita käytetään hyvin harvoin.

- Muistissa olevia operandeja manipuloidaan ohjeilla.

CISC-arkkitehtuurin edut

- Jokainen konekieliohje ryhmitellään mikrokoodikäskyiksi ja suoritetaan vastaavasti ja tallennetaan sitten sisäänrakennettuna pääprosessorin muistiin, jota kutsutaan mikrokoodin toteutukseksi.

- Koska mikrokoodimuisti on nopeampi kuin päämuisti, mikrokoodikäskyjoukko voidaan toteuttaa ilman huomattavaa nopeuden vähennystä kiinteään johdotettuun toteutukseen verrattuna.

- Koko uusi käskyjoukko voidaan käsitellä muuttamalla mikro-ohjelman rakennetta.

- CISC: n avulla ohjelman toteuttamiseen tarvittavien ohjeiden määrää voidaan vähentää rakentamalla rikkaita käskyjoukkoja, ja se voidaan myös saada käyttämään hitaampaa päämuistia tehokkaammin.

- Johtuen ohjeiden pääjoukosta, joka sisältää kaikki aikaisemmat ohjeet, tämä tekee mikrokoodauksesta helppoa.

CISC: n haitat

- Eri ohjeiden käyttämä kelloaika on erilainen - tästä johtuen - koneen suorituskyky hidastuu.

- Käskyjoukon monimutkaisuus ja sirulaitteisto lisääntyvät, kun prosessorin jokainen uusi versio koostuu alajoukosta aikaisemmista sukupolvista.

- Vain 20% olemassa olevista käskyistä käytetään tyypillisessä ohjelmointitapahtumassa, vaikka käytössä on monia erikoistuneita käskyjä, joita ei edes käytetä usein.

- Ehdolliset koodit asetetaan CISC-ohjeilla sivuvaikutuksena jokaiselle käskylle, joka vie aikaa tälle asetukselle - ja kun seuraava käsky muuttaa ehtokoodibittejä - kääntäjän on tutkittava ehtokoodibitit ennen tämän tapahtumista.

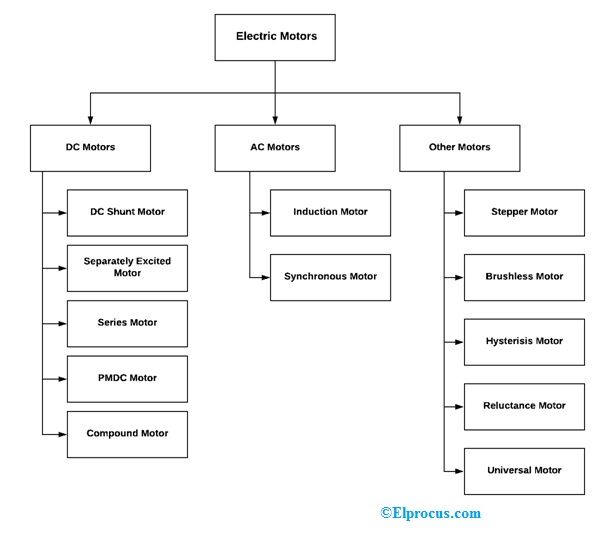

RISC vs. CISC

- Ohjelmoija voi estää tuhlaussyklit poistamalla tarpeettoman koodin RISC: stä, mutta samalla kun CISC-koodia käytetään, se johtaa tuhlaussykleihin CISC: n tehottomuuden vuoksi.

- RISC: ssä jokainen käsky on tarkoitettu pienen tehtävän suorittamiseen siten, että monimutkaisen tehtävän suorittamiseen käytetään useita pieniä käskyjä yhdessä, kun taas saman tehtävän suorittamiseen CISC: llä tarvitaan vain muutama käsky - koska se pystyy suorittamaan monimutkaisen tehtävän koska ohjeet ovat samanlaisia kuin korkean kielen koodi.

- CISC: tä käytetään tyypillisesti tietokoneisiin, kun taas RISC: tä käytetään älypuhelimiin, tabletteihin ja muihin elektronisiin laitteisiin.

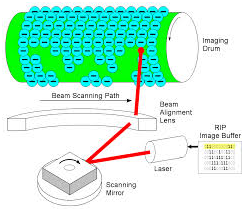

Seuraava kuva osoittaa enemmän eroja RISC: n ja CISC: n välillä

RISC vs. CISC

Siten tässä artikkelissa käsitellään RISC- ja CISC-arkkitehtuurien ominaisuuksia RISC- ja CISC-prosessoreiden arkkitehtuurien eduista ja haitoista sekä RISC- ja CISC-arkkitehtuurien eroista lyhyellä idealla. Jos haluat lisätietoja RISC- ja CISC-arkkitehtuureista, lähetä kyselysi kommentoimalla alla.

Valokuvahyvitykset:

- Suorittimen ohjeet arstechnica

- RISC-arkkitehtuuri lsi-kilpailu

- RISC vs. CISC mennessä csar-tehtävä