Kaksi pääasiallista FET-tyyppiä, joita tällä hetkellä on, ovat: JFETit ja MOSFETit.

MOSFETit voidaan edelleen luokitella ehtymistyypiksi ja parannustyyppi. Molemmat nämä tyypit määrittelevät MOSFETien perustavanlaatuisen toimintatavan, kun taas termi MOSFET itsessään on lyhenne metallioksidi-puolijohde-kenttävaikutteinen transistori.

Koska kahdella tyypillä on erilaiset työskentelyominaisuudet, arvioimme kumpikin erikseen eri artikkeleissa.

Ero parannuksen ja tyhjentämisen MOSFETin välillä

Pohjimmiltaan, toisin kuin lisälaitteiden MOSFET, tyhjentävät MOSFETit ovat päällä jopa 0 V: n läsnä ollessa portista lähteeseen -päätteiden (VGS) yli.

MOSFET-parannusta varten portista lähteeseen -jännitteen (VGS) on oltava yli portista lähteeseen -jännitteen (VGS (th)) jotta se toimisi .

N-kanavan tyhjennyksen MOSFET: n sen VGS (th) -arvo on kuitenkin yli 0 V. Tämä tarkoittaa, että vaikka VGS = 0 V, tyhjentävä MOSFET pystyy johtamaan virtaa. Sen sammuttamiseksi tyhjenemisen MOSFETin VGS on laskettava alle VGS: n (th) (negatiivinen).

Tässä artikkelissa keskustelemme MOSFET-ehtotyypistä, jonka sanotaan olevan ominaisuuksia, jotka vastaavat JFET: n ominaisuuksia. Samankaltaisuus on raja-arvon ja kylläisyyden välillä lähellä I: täDSS.

Perusrakentaminen

Kuvassa 5.23 on esitetty n-kanavan tyhjennystyyppisen MOSFETin sisäinen perusrakenne.

Voimme löytää lohkon p-tyyppistä materiaalia, joka on luotu piipohjalla. Tätä lohkoa kutsutaan substraatiksi.

Alusta on pohja tai perusta, jonka päälle MOSFET on rakennettu. Joillekin MOSFET-laitteille se on sisäisesti linkitetty 'lähde' -päätteeseen. Monet laitteet tarjoavat myös ylimääräisen lähdön SS-muodossa, jossa on 4-pääteinen MOSFET, kuten kuvassa 5.23 on esitetty

Tyhjennys- ja lähdeliittimet on kytketty johtavien koskettimien kautta n-seostettuihin paikkoihin ja kiinnitetty n-kanavan kautta, kuten samassa kuvassa on esitetty.

Portti on myös kytketty metallikerrokseen, vaikka se on eristetty n-kanavasta hienon piidioksidikerroksen (SiO) kauttakaksi).

SiOkaksion ainutlaatuinen eristysominaisuus, jota kutsutaan dielektriseksi, joka luo itsessään vastakkaisen sähkökentän vasteena ulkoisesti käytetylle sähkökentälle.

SiO-materiaali on eristävä kerroskaksitarjoaa meille seuraavat tärkeät tiedot:

Tämän materiaalin kanssa kehitetään täydellinen eristys portin terminaalin ja mosfet-kanavan välille.

Lisäksi se johtuu SiO: stakaksi, mosfetin portilla voi olla erittäin korkea tuloimpedanssi.

Tämän elintärkeän suuren tuloimpedanssin ominaisuuden vuoksi porttivirta IGon käytännössä nolla ampeeria kaikilla DC-esijännitetyillä MOSFET-kokoonpanoilla.

Perustoiminnot ja ominaisuudet

AS voidaan nähdä kuvasta 5.24, portti lähdejännitteelle on konfiguroitu nollavolttiin kytkemällä molemmat liittimet yhteen, kun taas jännite VDSkäytetään tyhjennys- ja lähdeliittimien poikki.

Yllä esitetyllä asetuksella tyhjennyspuoli muodostaa positiivisen potentiaalin n-kanavattomien elektronien kautta, samoin kuin vastaava virta JFET-kanavan kautta. Myös tuloksena oleva virta V.GS= 0V tunnistetaan edelleen nimellä IDSS, kuten on esitetty kuvassa 5.25

Voimme nähdä, että kuvassa 5.26 portin lähteen jännite VGSannetaan negatiivinen potentiaali -1 V: n muodossa.

Tämä negatiivinen potentiaali yrittää pakottaa elektroneja kohti p-kanavan substraattia (koska varaukset hylkäävät) ja vetää reikiä p-kanavan substraatista (koska vastakkaiset varaukset houkuttelevat).

Riippuen siitä, kuinka suuri tämä negatiivinen poikkeama VGSeli tapahtuu reikien ja elektronien rekombinaatio, mikä johtaa vapaiden elektronien pelkistymiseen johtamiseen käytettävissä olevassa n-kanavassa. Suurempi negatiivisen puolueellisuuden taso johtaa korkeampaan rekombinaatioasteeseen.

Tyhjennysvirta pienenee vastaavasti, kun yllä oleva negatiivinen esijännitetila kasvaa, mikä on osoitettu kuvassa 5.25 V: lleGSV: n tasotGS= -1, -2 ja niin edelleen, kunnes -6V: n puristusmerkki.

Tuloksena oleva tyhjennysvirta yhdessä siirtokäyräkaavion kanssa etenee aivan kuten a JFET.

Nyt positiivinen VGSarvot, portin positiivinen houkuttelee ylimääräisiä elektroneja (vapaita kantajia) p-tyyppisestä substraatista päinvastaisen vuotovirran vuoksi. Tämä muodostaa uusia kantajia tuloksena olevien törmäysten kautta kiihtyvien hiukkasten yli.

Kun portista lähteeseen -jännitteellä on taipumus nousta positiivisella nopeudella, tyhjennysvirta osoittaa nopeaa kasvua, mikä on osoitettu kuvassa 5.25 samoista syistä kuin edellä keskusteltiin.

V: n käyrien välille syntyi rakoGS= 0 V ja VGS= +1 osoittaa selvästi määrän, jolla virta kasvoi V: n 1 - V-vaihtelun vuoksiGS

Tyhjennysvirran nopean nousun takia meidän on oltava varovaisia maksimivirran suhteen, muuten se voi ylittää portin positiivisen jänniterajan.

Esimerkiksi kuvassa 5.25 kuvatun laitetyypin kohdalla VGS= + 4V aiheuttaisi tyhjennysvirran nousun 22,2 mA: lla, mikä saattaa ylittää laitteen enimmäisrikkorajan (virran).

Yllä oleva ehto osoittaa, että positiivisen portti-lähde-jännitteen käyttö tuottaa paremman vaikutuksen kanavan vapaiden kantoaaltojen määrään, toisin kuin kun VGS= 0 V.

Siksi tyhjennys- tai siirto-ominaisuuksien positiivinen hilajännitealue tunnetaan yleisesti nimellä parannusalue . Tämä alue on I: n raja-arvon ja kyllästystason välilläDSStai ehtymisalue.

Esimerkkiongelman ratkaiseminen

Edut ja sovellukset

Toisin kuin parannustilan MOSFETit, joissa tyhjennysvirta putoaa nollaan vasteena nollaportista lähteeseen -jännitteeseen, nykyaikaisessa tyhjennysmoodissa FET on havaittavissa oleva virta nollaporttijännitteellä. Tarkemmin sanottuna tyhjennys-lähde-vastus on yleensä 100 ohmia nollajännitteessä.

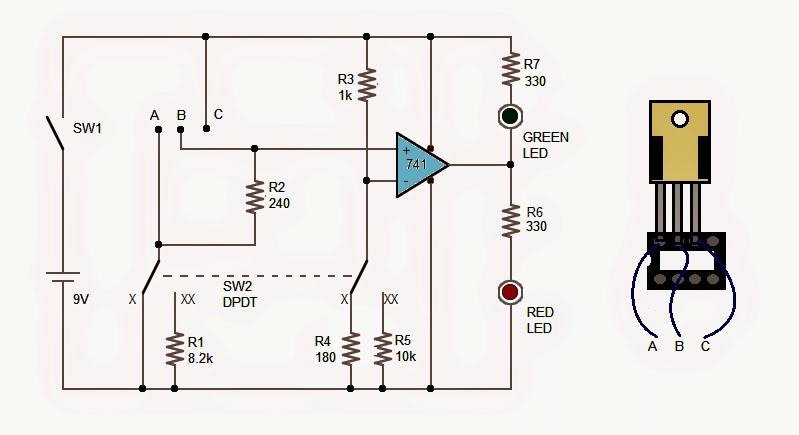

Kuten yllä olevasta kaaviosta käy ilmi, ON-resistanssi rds(päällä)vs. analoginen signaalialue näyttää käytännössä tasaiselta vasteelta. Tämä ominaisuus yhdessä näiden kehittyneen tyhjennystyyppisten laitteiden matalan kapasitanssitason kanssa antaa niiden olla erityisen ihanteellisia analogisina kytkiminä ääni- ja videokytkentäsovelluksissa.

Puutostilan MOSFET-ominaisuus 'on-on' -ominaisuuden ansiosta laite soveltuu täydellisesti yksittäisille FET-virtasäätimille.

Yksi tällainen esimerkkipiiri voidaan nähdä seuraavasta kuvasta.

Rs-arvo voidaan määrittää kaavalla:

Rs= VGSvinossa[1 - (minäD/ IDSS)1/2] / ID

missä MinäD on ulostulossa vaadittu säännellyn virran määrä.

Virtalähdekäytössä olevien tyhjentämismoodien tärkein etu on niiden minimaalinen tyhjenemiskapasitanssi, mikä tekee niistä sopivia esijännitekohteisiin matalan tulovirtauksen, keskinopeilla (> 50 V / us) piireillä.

Alla olevassa kuvassa on matalan sisäänmenon vuotovirtaerotus, joka käyttää kaksinkertaista matalavuototoimintoa FET.

Yleisesti ottaen JFET: n jompikumpi puoli tulee esijännitetyksi arvoon ID = 500 uA. Siksi kompensoinnin ja hajakapasitanssien lataamiseen käytettävissä oleva virta rajoitetaan 2ID: ään tai tällaisissa tapauksissa 1,0 mA: iin. JFET: n vastaavat ominaisuudet on todistettu tuotannossa ja varmistettu datalehdessä.

Cs symboloi tuloportaan 'hännän' virtalähteen lähtökapasitanssia. Tämä kapasitanssi on ratkaiseva ei-invertoivissa vahvistimissa, johtuen siitä, että tulovaiheessa tapahtuu merkittävää signaalinvaihtoa koko verkossa, ja latausvirrat Cs: ssä voivat olla suuria. Jos käytetään normaalia virtalähdettä, tämä hännän kapasitanssi voi olla selittävä huomattavasta kääntymisnopeuden heikkenemisestä ei-käänteisissä piireissä (verrattuna käänteisiin sovelluksiin, joissa latausvirrat Cs: ssä ovat yleensä vähäisiä).

Tappionopeuden lasku voidaan ilmaista seuraavasti:

1 / 1+ (Cs / Sc)

Niin kauan kuin Cs on pienempi kuin Cc (kompensointikondensaattori), kääntymisnopeudessa voi olla tuskin mitään vaihtelua. DMOS FET: n kanssa työskenneltäessä Cs voi olla noin 2 pF. Tämä strategia tuottaa valtavan parannuksen tappotaajuuteen. Jos tarvitaan yli 1–5 mA: n virtavajeita, laite voidaan esijännittää lisälaitetilaan tuottamaan jopa 20 mA enintään +2,5 V: n VGS: lle, ja minimaalinen lähtökapasitanssi on edelleen keskeinen näkökohta.

Seuraavassa alla olevassa sovelluksessa on asianmukainen parannustilan virtalähteen piiri.

Normaalisti päällä oleva analoginen kytkin voitaisiin rakentaa vaatimuksiin, joissa vakio-olosuhteet ovat tarpeen syöttöjännitevian aikana, esimerkiksi testityökalujen automaattisessa mittauksessa tai logiikkapiirien tarkan käynnistyksen varmistamiseksi kytkimen PÄÄLLÄ yhteydessä.

Laitteen alennettu negatiivinen kynnysjännite tarjoaa perusedellytykset taajuusmuuttajalle ja mahdollistaa työskentelyn pienellä jännitteellä.

Alla oleva piiri osoittaa yleiset esijännitystekijät kaikille ehtymismoodin DMOS-analogikytkimille.

Jotta laite sammuu, portilla tulee olla negatiivinen jännite. Tämän sanottuaan, on-resistanssi voitaisiin minimoida, kun FET: ää lisätään lisäksi käyttämällä positiivista hilajännitettä, mikä mahdollistaa sen erityisesti parannustilan alueella yhdessä tyhjenemismoodin alueen kanssa.

Tämä vastaus voidaan nähdä seuraavasta kaaviosta.

Yksikön korkeataajuusvahvistus yhdessä matalien kapasitanssiarvojen kanssa antaa kasvaneen 'ansioarvon'. Se on todella tärkeä osa VHF- ja UHF-vahvistuksia, jotka määrittelevät FET: n vahvistuksen kaistanleveystuotteen (GBW), joka voidaan kuvata seuraavasti:

GBW = gfs / 2 Pi (Csisään+ Culos)

p-kanavan tyhjennystyyppinen MOSFET

P-kanavan tyhjennystyyppisen MOSFETin rakentaminen on täydellinen käänteinen kuvassa 5.23 esitetystä n-kanavaversiosta. Merkitys on, että substraatti on nyt n-tyypin muotoinen ja kanavasta tulee p-tyyppi, kuten alla olevasta kuvasta 5.28a voidaan nähdä.

Liittimen tunniste pysyy muuttumattomana, mutta jännite ja virran napaisuus ovat päinvastaiset, kuten samassa kuvassa on esitetty. Tyhjennysominaisuudet olisivat täsmälleen kuvassa 5.25 kuvatut, lukuun ottamatta V: täDSmerkki, joka tällöin saa negatiivisen arvon.

Tyhjennysvirta IDosoittaa positiivista napaisuutta myös tässä tapauksessa, koska olemme jo kääntäneet sen suunnan. VGSosoittaa päinvastaisen, mikä on ymmärrettävää, kuten kuvassa 5.28c on esitetty.

Koska VGSon käännetty, tuottaa peilikuvan siirto-ominaisuuksille, kuten on esitetty kuvassa 528b.

Merkitys: tyhjennysvirta kasvaa positiivisessa V: ssäGSalue raja-arvosta V: ssäGS= Vp kunnes minäDSS, sitten se nousee edelleen V: n negatiivisena arvonaGSnousee.

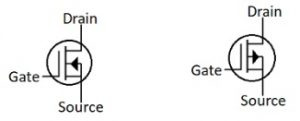

Symbolit

N- ja p-kanavan tyhjennystyyppisen MOSFETin graafiset merkit voidaan nähdä yllä olevasta kuvasta 5.29.

Tarkkaile tapaa, jolla valitut symbolit pyrkivät edustamaan laitteen todellista rakennetta.

Suoran yhteenliittämisen puuttumista (portin eristeen takia) portin ja kanavan välillä symboloi aukko portin ja symbolin eri napojen välillä.

Kanavaa edustava pystyviiva on kiinnitetty viemärin ja lähteen väliin ja substraatti 'pitää sitä'.

Yllä olevassa kuvassa on kaksi ryhmää symboleja jokaiselle kanavatyypille korostamaan sitä tosiasiaa, että joissakin laitteissa substraatti voi olla ulospäin ulottuvilla, kun taas toisissa tämä ei välttämättä näy.

MOSFET (parannustyyppi)

Vaikka ehtymis- ja parannustyyppiset MOSFET-laitteet näyttävät samanlaisilta sisäisen rakenteensa ja toimintamoodinsa suhteen, niiden ominaisuudet voivat olla melko erilaiset.

Suurin ero on tyhjennysvirta, joka riippuu portista lähteeseen -jännitteen tietylle tasolle katkaisutoimintaa varten.

N-kanavan parannustyyppinen MOSFET voi toimia positiivisen portti- / lähdejännitteen kanssa negatiivisten potentiaalien sijaan, jotka normaalisti voivat vaikuttaa tyhjennystyyppiseen MOSFETiin.

Perusrakentaminen

Voit visualisoida n-kanavan parannustyyppisen MOSFETin seuraavassa

Kuva 5.31.

P-tyyppinen materiaaliosa luodaan piipohjan kautta, ja kuten aiemmin on opittu, sitä kutsutaan substraatiksi.

Tämä substraatti on joissakin tilanteissa kiinnitetty sisäisesti lähdetapilla tyhjennystyyppiseen MOSFETiin, kun taas joissakin tapauksissa se on päätetty neljäntenä johtimena mahdollisen tason mahdollisen ulkoisen ohjauksen mahdollistamiseksi.

Lähde- ja tyhjennysliittimet liitetään tavalliseen tapaan käyttämällä metallikontakteja n-seostettuihin alueisiin.

Voi kuitenkin olla tärkeää visualisoida, että kuvassa 5.31 kanava kahden n-seostetun alueen välillä puuttuu.

Tätä voidaan pitää perustavanlaatuisena eroavuutena tyhjennystyyppisen ja parannustyyppisen MOSFETin sisäisen ulkoasun välillä, toisin sanoen sellaisen ominaiskanavan puuttumista, jonka oletetaan olevan osa laitetta.

SiO2-kerroksen voidaan nähdä olevan edelleen vallitsevaa, mikä varmistaa eristeen porttiterminaalin metallisen pohjan sekä viemärin ja lähteen välisen alueen välillä. Tässä voidaan kuitenkin todistaa seisovan erillään p-tyyppisestä materiaaliosasta.

Edellä esitetystä keskustelusta voidaan päätellä, että tyhjentävällä ja parannetulla MOSFET-sisäisellä asettelulla voi olla joitain yhtäläisyyksiä, paitsi että tyhjennyksen / lähteen välillä puuttuu kanava MOSFET-parannustyypille.

Perustoiminnot ja ominaisuudet

Parannustyypille MOSFET, kun 0 V syötetään sen VGS: ään, puuttuvan n-kanavan takia (jonka tiedetään kuljettavan paljon vapaita kantoaaltoja) aiheuttaa virtalähdön nollaksi, mikä on aivan toisin kuin tyhjennystyyppi MOSFET, jonka ID = IDSS.

Tällaisessa tilanteessa tyhjennys- / lähdeliittimien poissaolevan reitin puuttuessa suuria määriä elektronien muodossa olevia kantajia ei voida kerääntyä tyhjennykseen / lähteeseen (n-seostettujen alueiden takia).

Käyttämällä jonkin verran positiivista potentiaalia VDS: ssä, kun VGS on asetettu nollavolttiin ja SS-pääte on oikosulussa lähdepäätteellä, löydämme oikeastaan pari käänteistä puolueellista pn-liitosta n-seostettujen alueiden ja p-substraatin välillä mahdollistamaan merkittävä johtuminen poikki valuta lähteeseen.

Kuvassa 5.32 on esitetty tila, jossa VDS ja VGS syötetään positiivisella jännitteellä, joka on yli 0 V, jolloin tyhjennys ja portti voivat olla positiivisessa potentiaalissa lähteeseen nähden.

Portin positiivinen potentiaali työntää p-substraatin reiät SiO2-kerroksen reunaa pitkin lähtemään paikasta ja tunkeutuen syvemmälle p-substraatin alueille, kuten yllä olevassa kuvassa on esitetty. Tämä tapahtuu samankaltaisten varausten takia, jotka karkottavat toisiaan.

Tämän seurauksena tyhjennysalue syntyy lähelle SiO2-eristekerrosta, jossa on reikiä.

Tästä huolimatta p-substraattielektronit, jotka ovat materiaalin vähemmistökantajia, vedetään kohti positiivista porttia ja alkavat kerääntyä SiO2-kerroksen pinnan lähellä olevalle alueelle.

SiO2-kerroksen eristysominaisuuden vuoksi negatiiviset kantajat sallivat negatiivisten kantajien imeytymisen porttiterminaaliin.

Kun nostamme VGS: n tasoa, myös SiO2-pinnan lähellä oleva elektronitiheys kasvaa, kunnes vihdoin indusoitu n-tyypin alue pystyy sallimaan kvantifioitavan johtumisen koko viemärin / lähteen läpi.

VGS-suuruutta, joka aiheuttaa tyhjennysvirran optimaalisen kasvun, kutsutaan kynnysjännitteeksi, merkitty symbolilla VT . Datalehdissä näet tämän nimellä VGS (Th).

Kuten edellä on opittu, johtuen kanavan puuttumisesta VGS = 0: lla ja 'parannetulla' positiivisella portti-lähde-jännitesovelluksella, tämäntyyppiset MOSFET-laitteet tunnetaan parannustyyppisinä MOSFET-laitteina.

Tulet huomaamaan, että sekä tyhjennys- että parannustyyppisissä MOSFET-laitteissa on parannustyyppisiä alueita, mutta termi parannus käytetään jälkimmäiseen, koska se toimii erityisesti käyttämällä parannustoimintatilaa.

Nyt kun VGS työnnetään kynnysarvon yli, vapaiden kantajien pitoisuus kasvaa kanavassa, jossa se indusoituu. Tämä aiheuttaa tyhjennysvirran kasvun.

Toisaalta, jos pidämme VGS: n vakiona ja nostamme VDS (tyhjennys lähteeseen -jännitettä) -tasoa, se viime kädessä saa MOSFETin saavuttamaan kyllästymispisteen, kuten normaalisti tapahtuisi myös mille tahansa JFET: lle tai tyhjentävälle MOSFETille.

Kuten kuvassa 5.33 on esitetty, tyhjennysvirran ID tasoittuu puristusprosessin avulla, jonka kapeampi kanava osoittaa indusoidun kanavan tyhjennyspäähän.

Soveltamalla Kirchhoffin jännitelakia MOSFETin liittimien jännitteisiin kuvassa 5.33, saadaan:

Jos VGS pidetään vakiona tietyssä arvossa, esimerkiksi 8 V, ja VDS nousee 2: sta 5 V: iin, jännite VDG on Eq. 5.11: n voitiin nähdä laskevan välillä -6: sta -3 V: iin ja portin potentiaalin olevan yhä vähemmän positiivinen tyhjennysjännitteen suhteen.

Tämä vastaus estää vapaita kantajia tai elektroneja vetämästä kohti indusoidun kanavan tätä aluetta, mikä puolestaan johtaa kanavan tehollisen leveyden laskuun.

Viime kädessä kanavan leveys pienenee puristuspisteeseen saavuttaen kyllästystilan, joka on samanlainen kuin mitä olemme jo oppineet aikaisemmassa tyhjentämisessä MOSFET-artikkelissamme.

Tämä tarkoittaa, että VDS: n lisääminen edelleen kiinteällä VGS: llä ei vaikuta ID: n kyllästystasoon, kunnes piste, jossa hajoamistilanne saavutetaan.

Kuvaa 5.34 tarkasteltaessa voidaan tunnistaa, että MOSFETille, kuten kuvassa 5.333, jonka VGS = 8 V, saturaatio tapahtuu 6 V VDS-tasolla. Tarkemmin sanottuna VDS-kyllästystaso liittyy sovellettuun VGS-tasoon seuraavasti:

Epäilemättä se tarkoittaa siis sitä, että kun VT-arvo on kiinteä, VGS-tason nostaminen aiheuttaa verrannollisesti korkeammat kylläisyystasot VDS: lle kyllästystasojen lokuksen kautta.

Viitaten yllä olevassa kuvassa esitettyihin ominaisuuksiin, VT-taso on 2 V, mikä käy ilmi siitä, että tyhjennysvirta on pudonnut 0 mA: iin.

Siksi voimme tyypillisesti sanoa:

Kun VGS-arvot ovat pienempiä kuin parannustyyppisen MOSFETin kynnysarvo, sen tyhjennysvirta on 0 mA.

Voimme myös selvästi nähdä yllä olevasta kuvasta, että niin kauan kuin VGS nostetaan korkeammaksi VT: stä 8 V: een, vastaava ID: n kyllästystaso nousee myös 0: sta 10 mA: n tasoon.

Lisäksi voimme edelleen huomata, että VGS-tasojen välinen tila kasvaa VGS: n arvon kasvaessa aiheuttaen tyhjennysvirran loputtomasti kasvavia lisäyksiä.

Havaitsemme, että tyhjennysvirran arvo liittyy VGS-tasojen portti-lähde-jännitteeseen, joka on suurempi kuin VT, seuraavan epälineaarisen suhteen kautta:

Neliösulkuina esitetty termi on termi, joka vastaa epälineaarisesta suhteesta ID: n ja VGS: n välillä.

Termi k on vakio ja se on MOSFET-asettelun funktio.

Voimme selvittää tämän vakion k arvon seuraavan yhtälön avulla:

missä ID (päällä) ja VGD (päällä) ovat kumpikin arvot nimenomaan laitteen ominaisuuksista riippuen.

Seuraavassa kuvassa 5.35 havaitaan, että tyhjennys- ja siirto-ominaisuudet on järjestetty vierekkäin selventämään siirtoprosessia toistensa suhteen.

Pohjimmiltaan se on samanlainen kuin aiemmin selitetty prosessi JFET: lle ja tyhjennystyyppisille MOSFET: ille.

Tässä tapauksessa on kuitenkin muistettava, että tyhjennysvirta on 0 mA VGS VT: lle.

Täällä ID voi nähdä huomattavan määrän virtaa, joka kasvaa Eq: n määrittämällä tavalla. 5.13.

Huomaa, että kun määritämme siirtofunktioiden pisteet tyhjennysominaisuuksista, otamme huomioon vain kyllästystasot. Tämä rajoittaa toiminta-alueen VDS-arvoihin, jotka ovat korkeammat kuin kyllästystasot, jotka on määritetty Eq. (5.12).

p-kanavan parannustyyppiset MOSFETit

Kuvassa 5.37a esitetty p-kanavan parannustyyppisen MOSFETin rakenne on aivan päinvastainen kuin kuvassa 5.31.

Merkitys, nyt huomaat, että n-tyyppinen substraatti ja p-seostetut alueet viemäri- ja lähdeliitosten alla.

Liittimet ovat edelleen vakiintuneita, mutta kukin nykyinen suunta ja jännitteen napaisuus ovat päinvastaiset.

Tyhjennysominaisuudet voivat näyttää kuten kuvassa 5.37c on annettu, ja niiden virran määrä kasvaa jatkuvasti negatiivisempien VGS-voimakkuuksien vuoksi.

Siirtymisominaisuudet olisivat kuvan 5.35 siirtokäyrän peilivaikutelma (ID-akselin ympärillä), jonka ID kasvaisi yhä useammilla negatiivisilla VGS-arvoilla VT: n yläpuolella, kuten kuvassa 5.37b on esitetty. Yhtälöt (5.11) - (5.14) ovat vastaavasti sopivia p-kanavalaitteisiin.

Viitteet:

- https://fi.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Pari: Anti Spy RF -ilmaisinpiiri - langaton virheenilmaisin Seuraava: Siirrä ominaisuudet