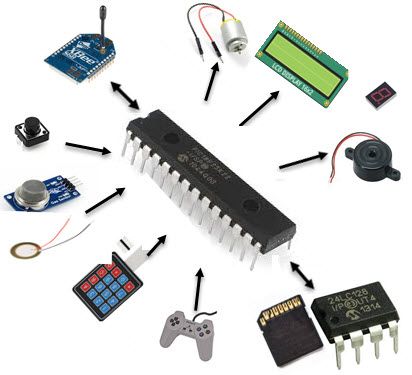

Oli aikakausi, jolloin tietokoneet olivat kooltaan niin mammutteja, että niiden asentamiseen tarvittiin helposti huonetilaa. Mutta tänään ne ovat niin kehittyneitä, että voimme jopa kuljettaa niitä kannettavina helposti. Tämän mahdollistanut innovaatio oli integroitujen piirien käsite. Sisään Integroidut piirit , suuri määrä aktiivisia ja passiiviset elementit yhdessä niiden yhteenliitäntöjen kanssa kehitetään pienellä piikiekolla, tyypillisesti 50 - 50 mil poikkileikkaukseltaan. Perusprosesseja, joita noudatetaan tällaisten piirien tuotannossa, ovat epitaksiaalinen kasvu, naamioitu epäpuhtauksien diffuusio, oksidikasvu ja oksidien syövytys käyttäen fotolitografiaa kuvion tekemiseksi.

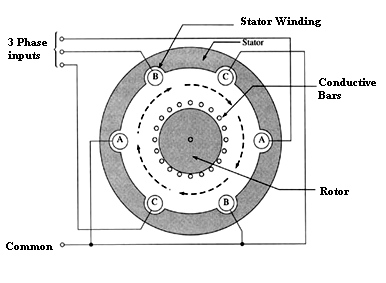

Kiekon päällä olevat komponentit sisältävät vastukset, transistorit, diodit, kondensaattorit jne. ... Monimutkaisin elementti IC: n yli valmistettavaksi on transistorit. Transistorit ovat erityyppisiä kuten CMOS, BJT, FET. Valitsemme tyypin transistoritekniikan käyttöön IC: n yli vaatimusten perusteella. Tässä artikkelissa tutustutaan käsitteeseen CMOS-valmistus (tai) transistorien valmistaminen CMOS: na.

CMOS-valmistus

Vähemmän virrankulutusta CMOS-tekniikka käytetään transistorien toteuttamiseen. Jos tarvitsemme nopeamman piirin, transistorit toteutetaan yli IC käyttämällä BJT . Valmistus CMOS-transistorit IC: t voidaan tehdä kolmella eri menetelmällä.

N-kuopan / P-kuopan tekniikka, jossa n-tyyppinen diffuusio tehdään p-tyyppiselle substraatille tai p-tyyppinen diffuusio tapahtuu vastaavasti n-tyyppiselle substraatille.

Kaksikaivoinen tekniikka , missä NMOS ja PMOS-transistori kehitetään kiekon yli samanaikaisella diffuusiolla epitaksiaalisen kasvupohjan yli substraatin sijasta.

Silicon On Insulator -prosessi, jossa piin käyttämisen sijaan substraattina käytetään eristemateriaalia nopeuden ja tarttumisalttiuden parantamiseksi.

N- / P-kaivotekniikka

CMOS voidaan saada integroimalla molemmat NMOS- ja PMOS-transistorit samalla piikiekolla. N-kaivotekniikassa n-tyyppinen kaivo diffundoituu p-tyyppiselle alustalle, kun taas P-kaivossa se on päinvastoin.

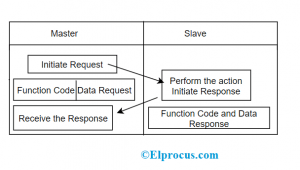

CMOS-valmistusvaiheet

CMOS-valmistusprosessi virtaus suoritetaan käyttäen kaksikymmentä perusvalmistusvaihetta samalla, kun se valmistetaan N- / P-kaivotekniikalla.

CMOS: n tekeminen N-kuopalla

Vaihe 1: Ensin valitaan substraatti valmistuksen perustaksi. N-kuoppaa varten valitaan P-tyyppinen piialusta.

Alusta

Vaihe 2 - Hapetus: N-tyyppisten epäpuhtauksien selektiivinen diffuusio suoritetaan käyttämällä Si02: ta esteenä, joka suojaa kiekon osia substraatin likaantumiselta. SiOkaksilevitetään hapetusprosessilla, jolloin substraatti altistetaan korkealaatuiselle hapelle ja vedylle hapetuskammiossa noin 1000 ° C: ssa0c

Hapetus

Vaihe 3 - Fotoresistin kasvaminen: Tässä vaiheessa selektiivisen syövytyksen mahdollistamiseksi Si02-kerrokselle tehdään fotolitografiaprosessi. Tässä prosessissa kiekko on päällystetty yhtenäisellä kalvolla valoherkästä emulsiosta.

Fotoresistin kasvu

Vaihe 4 - Peittäminen: Tämä vaihe on fotolitografiaprosessin jatko. Tässä vaiheessa haluttu avoimuusmalli tehdään kaavain. Tätä stensiiliä käytetään maskina fotoresistin päällä. Substraatti on nyt alttiina UV-säteet maskin paljaiden alueiden alla oleva fotoresisti polymeroituu.

Fotoresistin naamiointi

Vaihe 5 - Valottamattoman fotoresistin poisto: Naamio poistetaan ja valoresistin valottamaton alue liuotetaan kehittämällä kiekko käyttämällä kemikaalia, kuten trikloorietyleeniä.

Fotoresistin poisto

Vaihe 6 - Etsaus: Vohveli upotetaan fluorivetyhapon syövytysliuokseen, joka poistaa oksidin alueilta, joiden läpi lisäaineita on tarkoitus diffundoida.

SiO2: n etsaus

Vaihe 7 - Koko fotoresistikerroksen poisto: Aikana syövytysprosessi , ne eivät vaikuta Si02: n osiin, jotka on suojattu fotoresistikerroksella. Fotoresistinaamio erotetaan nyt kemiallisella liuottimella (kuuma H2SO4).

Fotoresistikerroksen poisto

Vaihe 8 - N-kuopan muodostus: N-tyyppiset epäpuhtaudet diffundoituvat p-tyyppiseen substraattiin paljaan alueen läpi muodostaen siten N-kuopan.

N-kuopan muodostuminen

Vaihe 9 - SiO2: n poisto: Si02-kerros poistetaan nyt fluorivetyhapolla.

SiO2: n poisto

Vaihe 10 - Polysilikon laskeuma: A. Portin väärä suuntaus CMOS-transistori johtaisi ei-toivottuun kapasitanssiin, joka voisi vahingoittaa virtapiiriä. Joten tämän 'itsestään kohdistuvan porttiprosessin' estämiseksi on edullista, kun porttialueet muodostetaan ennen lähteen ja tyhjennyksen muodostumista ioni-implantointia käyttäen.

Polysilikon kerrostuminen

Polysilikonia käytetään portin muodostamiseen, koska se kestää yli 8000 korkean lämpötilan0c, kun kiekolle tehdään hehkutusmenetelmiä lähteen ja tyhjennyksen muodostamiseksi. Monikiteinen pii kerrostetaan käyttämällä Kemiallinen kerrostamisprosessi ohut kerros porttioksidia. Tämä ohut porttioksidi polysilikerroksen alla estää lisädopointia porttialueen alla.

Vaihe 11 - Gate-alueen muodostaminen: Lukuun ottamatta kahta aluetta, joita tarvitaan portin muodostamiseen NMOS- ja PMOS-transistorit jäljelle jäänyt osa poly- piitä erotetaan.

Porttialueen muodostuminen

Vaihe 12 - Hapetusprosessi: Hapettumiskerros kerrostetaan kiekon päälle, joka toimii suojana edelleen diffuusio- ja metallointiprosessit .

Hapetusprosessi

Vaihe 13 - Peittäminen ja diffuusio: Alueiden valmistamiseksi n-tyyppisten epäpuhtauksien diffuusiota varten käyttämällä peittoprosessia tehdään pieniä aukkoja.

Naamiointi

Diffuusiomenetelmää käyttämällä kehitetään kolme n + -aluetta NMOS-päätelaitteiden muodostamiseksi.

N-diffuusio

Vaihe 14 - oksidin poisto: Oksidikerros irrotetaan.

Oksidin poisto

Vaihe 15 - P-tyypin diffuusio: Samoin kuin n-tyyppinen diffuusio PMOS-päätteiden muodostamiseksi, suoritetaan p-tyyppinen diffuusio.

P-tyypin diffuusio

Vaihe 16 - Paksun kentän oksidin asettaminen: Ennen metalliterminaalien muodostamista päällystetään paksu kenttäoksidi muodostamaan suojakerros kiekon alueille, joissa päätteitä ei tarvita.

Paksu kenttäoksidikerros

Vaihe 17 - Metallointi: Tätä vaihetta käytetään muodostamaan metalliliittimiä, jotka voivat tarjota yhteenliitäntöjä. Alumiini levitetään koko kiekolle.

Metallointi

Vaihe 18 - Ylimääräisen metallin poisto: Ylimääräinen metalli poistetaan kiekosta.

Vaihe 19 - Terminaalien muodostaminen: Ylimääräisen metallin poistamisen jälkeen muodostetuissa rakoissa muodostetaan liittimiä yhteenliitäntöjä varten.

Terminaalien muodostaminen

Vaihe 20 - Päätteen nimien määrittäminen: Nimet määritetään NMOS- ja PMOS-transistorit .

Terminaalien nimien määrittäminen

CMOS: n tekeminen P-kuoppatekniikalla

P-kuopan prosessi on samanlainen kuin N-kuopan prosessi paitsi, että tässä käytetään n-tyyppistä substraattia ja suoritetaan p-tyyppisiä diffuusioita. Yksinkertaisuuden vuoksi N-kaivoprosessi on edullinen.

CMOS: n kaksoisputken valmistus

Kahden putken prosessia käyttämällä voidaan hallita P- ja N-tyyppisten laitteiden vahvistusta. Eri vaiheet, jotka liittyvät CMOS: n valmistus käyttäen Twin-tube-menetelmää ovat seuraavat

- Otetaan kevyesti seostettu n- tai p-tyyppinen substraatti ja käytetään epitaksiaalista kerrosta. Epitaksiaalikerros suojaa sirun lukitusongelmaa.

- Kasvatetaan erittäin puhtaita piikerroksia, joilla on mitattu paksuus ja tarkka lisäaineen pitoisuus.

- Putkien muodostuminen P- ja N-kuoppia varten.

- Ohut oksidirakenne suojaa likaantumiselta diffuusioprosessien aikana.

- Lähde ja tyhjennys muodostetaan ioni-implantointimenetelmillä.

- Leikkauksia tehdään osien valmistamiseksi metallikontakteille.

- Metallointi tehdään metallikontaktien vetämiseksi

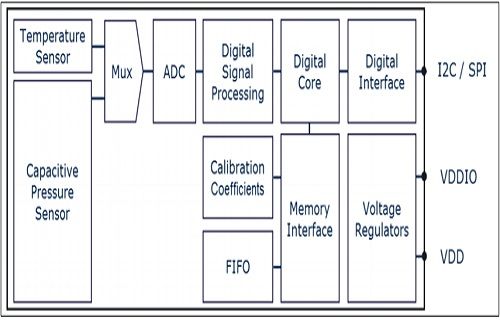

CMOS-IC-asettelu

Yläkuva CMOS: iin valmistus ja asettelu on annettu. Tässä voidaan nähdä erilaisia metallikoskettimia ja N-kaivon diffuusioita.

CMOS-IC-asettelu

Näin ollen kyse on kaikesta CMOS-valmistustekniikat . Tarkastellaan 1 neliön levyistä kiekkoa, joka on jaettu 400 siruun, joiden pinta-ala on 50 mil 50 mil. Transistorin valmistaminen vie 50 mil2: n alueen. Siksi kukin IC sisältää 2 transistoria, joten jokaiseen kiekkoon on rakennettu 2 x 400 = 800 transistoria. Jos jokaisessa erässä käsitellään 10 kiekkoa, voidaan samanaikaisesti valmistaa 8000 transistoria. Mitä komponentteja olet havainnut IC: llä?